Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Комбинационные схемы, сумматоры и умножители

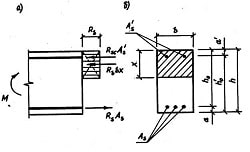

Комбинационная логика (комбинационная схема) в теории цифровых устройств — двоичная логика функционирования устройств комбинационного типа. Цифровая схемотехника существенно отличается от аналоговой. При распространении логических сигналов по цифровой схеме они не затухают. На них до определенного предела не воздействуют шумы и помехи. Это является несомненным преимуществом цифровой схемотехники. В результате возникло большое количество видов цифровых микросхем. Все цифровые устройства разделяются на две большие группы: комбинационные схемы и последовательностные. Комбинационные схемы — это устройства без памяти. Выходные сигналы этого вида цифровых схем зависят только от текущей комбинации входных логических сигналов, как это показано на рисунке 25, и не зависят от их предыдущих значений.

Рис.25. Функциональная схема цифрового комбинационного устройства

Схема, приведенная на рисунке 25, показывает, что на вход подается M сигналов, а на выходе из них формируется K выходных сигналов. При этом во внутренней схеме не должно быть обратных связей, как это показано на рисунке 26.

Рис. 26. Пример реализации комбинационного устройства на логических элементах

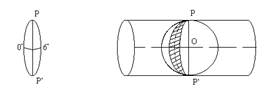

Наиболее распространенными комбинационными устройствами являются дешифраторы, шифраторы, семисегментные дешифраторы, мультиплексоры и демультиплексоры, арифметические сумматоры и арифметико-логические устройства (АЛУ). Дешифраторы предназначаются для преобразования двоичного или двоично-десятичного кода в любой другой код. В качестве отдельных микросхем сейчас дешифраторы практически не применяются. В настоящее время двоичные дешифраторы вместе с мультиплексорами используются в составе микросхем памяти (ОЗУ и ПЗУ) для обращения к конкретной ячейке памяти. Особенностью двоичного дешифратора является то, что логический сигнал появляется только на выходе, соответствующем номеру двоичной комбинации. Условно-графическое обозначение дешифратора приведено на рисунке 27.

Рис. 27. Условно-графическое обозначение дешифратора

Еще одним распространенным цифровым комбинационным устройством является двоичный сумматор. Он применяется в составе арифметико-логического устройства (АЛУ), которое является основным блоком микропроцессора, входит в состав диспетчера памяти практически всех современных компьютеров, работает внутри цифровых фильтров. На рисунке 29 приведено условно-графическое обозначение микросхемы К155ИМ3 — четырехразрядного сумматора.

Рис. 29. Условно-графическое обозначение сумматора

|

||||

|

Последнее изменение этой страницы: 2021-07-18; просмотров: 157; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.93.123 (0.005 с.) |