Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Способы представления логических переменных электрическими сигналамиСтр 1 из 3Следующая ⇒

ЛОГИЧЕСКИЕ СХЕМЫ 8.1 Основные определения Электронные схемы, построенные только на логике, называют комбинационными. Выход или выходы зависят только от комбинации переменных на входах. В отличие от них схемы, содержащие элементы памяти (например, триггеры), называют последовательностными. Последовательностные, так как выход (выходы) зависят не только от комбинации переменных, но и от состояния элементов памяти (последовательности записи в них).

Выделяют три основных вида логических элементов: 1. Выполняют операцию сложения (сумматор). Дизъюнкция. Логическое «ИЛИ».

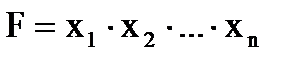

2 Выполняют операцию умножения. Конъюнкция. Логическое «И».

3 Выполняют отрицание. Логическое «НЕ».

Логические элементы, реализующие эти операции, называют простейшими, а те, которые содержат несколько простейших, называют комбинированными.

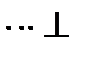

Диодные логические схемы Это самые простые схемы, имеют наивысшую помехоустойчивость. Число входов в среднем достигает десяти. Нагрузкой обычно является один элемент. Имеется в виду, что нагрузка – точно такой же ЛЭ. Малая нагрузочная способность потому, что эти схемы относятся к пассивным, в них нет усилителей мощности. Частотный диапазон невысокий (до 1 МГц), так как объединенные параллельные диодные входы эквивалентны объединению параллельных конденсаторов, которые заряжаются, разряжаются. На это необходимо время, снижается быстродействие. На рис. 8.6 представлена диодно–логическая схема сложения. Возможны два состояния: 1 Входы соединены с землей через открытые выходы таких же логических схем. Иногда принимают это состояние эквивалентным соединению всех входов с землей посредством проводников. 2 Для того, чтобы открыть диоды необходимо подать напряжение, уровень которого в несколько раз больше зоны нечувствительности диодов. 5 В – минимальное стандартное напряжение, но оно может быть и 500 В и 5 кВ, если диоды высоковольтные. В этом случае и нагрузочная способность может быть больше единицы, но потребление схем становится большим.

Рис. 8.7 Диодная схема логического сложения

Схема работает следующим образом. Принимаем, что на вход Х1 подается высокий уровень напряжения, который называется единицей. Этот уровень должен поступать с выхода точно такой же логической схемы, или каким–то другим способом, имитирующим те же условия. Но так как единица поступает только на вход Х1, то на остальных входах Х2…Хn должны быть нули. Они тоже должны быть организованы выходами таких же логических схем. В простейшем случае это могут быть проводники (перемычки), соединяющие входы Х2…Хn с землей. Следовательно, диод VD1 будет открыт, высокий уровень Х1 через VD1 проходит на выход, на котором выделяется также этот высокий уровень, из которого вычитается падение напряжения на диоде, т.е. на выходе будет уже меньший высокий уровень, тем не менее, его называют единицей. Диоды VD2… VDn в это время будут закрыты, так как на входах Х2…Хn низкие уровни, их барьерные емкости включены параллельно, накапливают заряд.

Если теперь подать высокий уровень на вход Х2, то откроется VD2 но состояние выхода F почти не изменится, т.е. там сохраняется высокий уровень – единица. То же самое будет при подаче единицы на все входы одновременно. Таким образом, удовлетворяется операция логического сложения. Принцип двойственности состоит здесь в том, что если единицами назвать низкие уровни на входах и на выходе, то эта логическая схема сложения будет выполнять логическую операцию умножения (см. рисунок 2.2). Физический смысл заключается в том, что низкий уровень на выходе, который назван единицей, будет только в том случае, если на всех входах одновременно будут низкие уровни, которые тоже названы единицами. На рис. 8.8 представлена диодная схема логического умножения. Если все диоды закрыты высокими уровнями (единицами), то ток протекает по цепи

Рис. 8.8 Диодная схема логического умножения

Принцип двойственности: Если низкий уровень на входе назвать единицей, то низкий уровень на выходе тоже единица будет в том случае, когда хотя бы на одном любом входе будет “1”. Широко применяется схема умножения в ИМС 533, 555 серии.

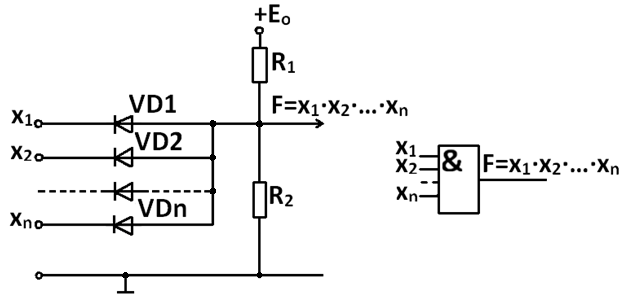

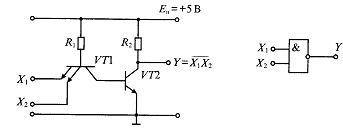

8.4 Логические схемы ТТЛ Типичный представитель этих микросхем – 155 серия. Она уже не выпускается, но так как основные схемные решения те же, что и в более современных, отличие только в особенностях, то есть смысл, с учебной целью, начать рассмотрение именно этой логической схемы. Кстати, микросхемы 155 серии взаимозаменяемы с более современными. Основные параметры: – напряжение питания +5 В (современные ТТЛ схемы – 2…3В); – уровень нуля в диапазоне от +0,05 до +0,4 В; – уровень единицы в диапазоне от +2,4 до +4,9 В; – помехоустойчивость средняя – это диапазон между нижним уровнем единицы и верхним уровнем нуля; – потребление среднее (1 – 10 мВт); – среднее время задержки 10 нс; – температурный диапазон –10 – +70 °C; В ИМС, выполненных по технологии ТТЛ, в качестве базового элемента используется многоэмиттерный транзистор. Упрощенная схема логического элемента И-НЕ с многоэмиттерным транзистором VT1 приведена на рис. 8.9. Многоэмиттерный транзистор (МЭТ) отличается от обычного транзистора тем, что он имеет несколько эмиттеров, расположенных так, что прямое взаимодействие между ними исключается. Благодаря этому переходы база-эмиттеры МЭТ можно рассматривать как параллельно включенные диоды. Второй транзистор VТ2 является инвертором сигнала, выполняющим функцию НЕ. Если хотя бы на один эмиттер МЭТ подан низкий уровень, то ток базы VT2 равен нулю и на коллекторе VT2 будет высокий уровень. Для того чтобы напряжение на коллекторе VT2 имело низкий уровень, необходимо на все эмиттеры МЭТ податъ высокий уровень. Благодаря этому алгоритму реализуется функция И-НЕ. В более поздних сериях

Рис. 8. 9. Упрощенная схема логического элемента 2И-НЕ (ТТЛ)

ИМС, выполненных по технологии ТТЛ, использовался сложный инвертор с двуполярным ключом, а для исключения насыщения МЭТ применялись диоды Шотки с малым падением напряжения в прямом направлении (ТТЛШ). Принципиальная схема одной из логических ТТЛ–схем ЛА-3 изображена на рис. 8.10. В корпусе схемы размещены четыре совершенно одинаковых узла. На его поверхности, сверху или снизу располагается метка (точка или вмятина). Смотреть на микросхему (корпус) надо снизу, на электроды, считать от метки по часовой стрелке. Седьмой электрод предназначен для подключения минуса источника питания, четырнадцатый – для плюса. По такому же принципу производится отсчет электродов и в других, более сложных случаях.

Рис. 8.10 ТТЛ логическая схема: а – схема ЛА-3; б – цоколевка микросхемы

Элемент И-НЕ может быть представлен последовательным соединением трех каскадов: · Входного многоэмиттерного транзистора VT 1с резистором R 1 и диодами VD 1 – VD 2, реализующий логическую функцию И; · Фазорасщепителя на транзисторе VT2, резисторе R4 и цепи нелинейной коррекции R2, R3 и VT3; · Двухтактного выходного усилителя на транзисторах VT4 и VT5, резисторе R5 и диоде VD3.

Диоды VD1 и VD2 имеют два назначения: 1 Противозвонное назначение. Смысл в том, что при переходе от нуля к единице или наоборот возникают колебательные процессы. И эти колебательные процессы затухают быстрее, если есть диоды VD1, VD2. 2 Входы ЛЭ не допускают даже кратковременную подачу отрицательных уровней, но иногда такое случается. Диоды их закорачивают, защищают входы. VT1 – многоэмиттерный транзистор. Каждый отдельный эмиттер – отдельный вход. Количество в среднем до десяти, т. е. эта схема содержит усилительные элементы в отличие от предыдущей, поэтому к выходу можно подключить до десяти точно таких же логических схем. Рассмотрим работу элемента И-НЕ. Допустим, что хотя бы один из входов Х1 или Х2 подключен к общей шине, т.е. на него подано напряжение логического «нуля». В этом случае многоэмиттерный транзистор VT 1 оказывается насыщен током, протекающим через резистор R 1. Напряжение на его коллекторе будет мало отличаться от нулевого. Поэтому транзистор VT 2 фазорасщепителя оказывается запертым. Так как эмиттерный ток транзистора VT 2 практически равен нулю, будет заперт и транзистор VT 5. Ток, протекающий через резистор R 4, втекает в базу транзистора VT 4, насыщая его. Поэтому напряжение, присутствующее на выходе F, близко к напряжению питания и определяется выражением U 1 вых= U п – I вых R 5 – U КЭ VT4 – U VD3. (8.6) Таким образом, при наличии на любом из входов схемы напряжения низкого уровня, напряжение на его выходе будет иметь высокий уровень. Предположим теперь, что на все входы логического элемента подан высокий уровень напряжения. В этом случае все эмиттерные переходы транзистора VT 1 оказываются запертыми. При этом его коллекторный переход смещается в прямом направлении по цепи резистор R 1, коллекторный переход транзистора VT 1 и последовательно соединенные эмиттерные переходы транзисторов VT 2 и VT 5 будет протекать ток. Этот ток насытит транзисторы VT 4 и VT 5, и на выходе F логического элемента установится низкое напряжение, численно равное напряжению насыщения транзистора VT 5:

U0вых = UКЭ VT5 = Iвых rвых VT5. (8.7)

Так как транзистор VT 2 насыщен, присутствующее на его коллекторе напряжение оказывается недостаточным для прямого смещения двух последовательно включенных p - n - переходов (эмиттерный переход транзистора VT 4 и диода VD 3). Транзистор VT 4 будет заперт. Таким образом, если на всех входах логического элемента «штрих Шеффера» присутствует высокое напряжение, на выходе логического элемента будет напряжение низкого уровня.

Из приведенного описания следует, что в общем случае параллельное соединение нескольких выходов таких элементов недопустимо, так как формирование на них сигналов различных уровней приведет к выходу из строя транзисторов выходного усилителя мощности. Параллельно можно соединять только выходы синхронно работающих элементов. Схема реализует логическую функцию И-НЕ. Укажем конкретное назначение отдельных элементов схемы. Исполнение выходного каскада по двухтактной схеме позволяет решить одновременно две задачи:

Во входной цепи многоэмиттерного транзистора VT 1 включены дополнительные диоды VD 1и VD 2, которые защищают элемент от появления на его входе недопустимых напряжений обратной полярности. Нелинейная цепь коррекции R 2, R 3, VT 3позволяет увеличить быстродействие элемента и приблизить его переходную характеристику (АПХ) к прямоугольной. Последнее качество улучшает формирующие свойства элемента. Рассмотрим его работу. Принцип действия данной цепи основан на зависимости её сопротивления от состояния транзистора VT 5. Если этот транзистор заперт, то транзистор нелинейной цепи коррекции VT 3 также заперт. Суммарное сопротивление цепи, шунтирующей эмиттерный переход транзистора VT 5, в основном определяется сопротивлением резистора R2, которое велико. Поэтому на начальном этапе формирования на выходе элемента напряжения логического «0» весь эмиттерный ток транзистора VT 2 втекает в базу VT 5, что форсирует его включение. После включения VT 5 насыщается и VT 3, шунтируя эмиттерный переход VT 5 низкоомным сопротивлением R 4. Это, во-первых, уменьшает степень насыщения транзистора VT 5 и, во-вторых, при последующем выключении увеличивает ток, удаляющий из базовой области этого транзистора избыточный заряд неосновных носителей. Оба этих фактора способствуют снижению времени рассасывания транзистора VT 5, что повышает быстродействие логического элемента ЛЭ. Следует отметить, что в момент переключения ЛЭ в его выходной цепи протекает так называемый «сквозной ток», обусловленный тем, что в течении интервала рассасывания запираемого транзистора оба транзистора выходного двухтактного усилителя оказываются насыщенными. Это приводит к тому, что потребления имеет явно выраженный импульсный характер. Поэтому с увеличением частоты переключения среднее значение тока, потребляемого элементом, возрастает. Растет и его суммарная потребляемая мощность. Кроме того, протекание импульсов тока за счет действия индуктивности соединительных проводов (Lпр на рис. 2.4б), что может привести к появлению ложных срабатываний соседних элементов (внутренние помехи).

Для ограничения величины «сквозного тока» в коллекторную цепь транзистора VT 4 включен резистор R 5. Однако чрезмерное увеличение сопротивления этого резистора, во-первых, увеличивает мощность, рассеиваемую в элементе, и, во-вторых, уменьшает нагрузочную способность. Поэтому для исключения действия помех шины питания должны выполняться с малой собственной индуктивностью и по всей длине шунтироваться дополнительными конденсаторами С доп с малой паразитной индуктивностью (как правило, керамическими)(рис. 8.11). Использование такого технического решения позволяет свести к минимуму действия на устройство внутренних помех.

Рис. 8.11 Шунтирование шины питания Логического элемента ТТЛ дополнительными конденсаторами

Следует отметить еще одну особенность применения ЛЭ ТТЛ. Согласно приведенному алгоритму работы, если вход остается неподключенным к источнику сигнала, можно считать, что на него подан сигнал логической «1». На практике неиспользуемые входы элементов ТТЛ рекомендуется не оставлять свободными, а через дополнительный резистор R доп подключать к выводу +Uп. в противном случае, так в состоянии логической «1» по входу элемент обладает большим входным сопротивлением, резко увеличивается вероятность воздействия на него помех, что снижает надежность работы логического устройства. Обычно один резистор используется для подключения нескольких входов ЛЭ. В этом случае его сопротивление может быть найдено из условия

Резистор R1 устанавливает необходимую величину базового тока VT1 (≈4кОм).

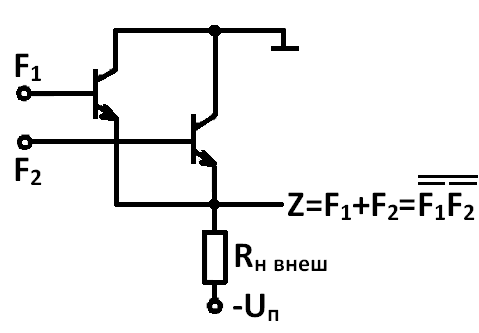

Объединение выходов Для объединения выходов используется микросхема (см. рис. 8.12) с открытым коллектором (бывает с открытым эмиттером).

Рис. 8.12 Микросхема с открытым коллектором

Выходы этих микросхем можно соединить друг с другом, но величину тока необходимо рассчитывать по наихудшему случаю. Обычно последовательно с коллекторным электродом включают элементы индикации, светодиоды, обмотки реле, цепи других логических элементов. Если на входы подавать импульсы, то на выходе в этом виде импульсов не будет, так как нет напряжения. Чтобы наблюдать импульсы, необходимо дополнить схему резистором R. Тогда в цепи этого резистора и транзистора VT4 появится импульсный ток, а на экране осциллографа импульсы напряжения. Допустимые величины тока для ЛА7 – 15 мА, ЛА8 – 5 мА. Ромбик с подставкой означает открытый коллектор. Последующие серии ТТЛ являются развитием 155 серии. Эти микросхемы взаимозаменяемы, в том числе и с 155 серией. Они обладают большей мощностью, так как на выходе находятся составные транзисторы. Величина коэффициента разветвления может достигать 20, это значит, что можно подключать до 20 таких же логических схем. Обладают повышенным быстродействием: 5 ÷ 6 нс. Применяются диоды и транзисторы Шоттки. В действительности транзистора Шоттки нет, есть схема, представленная на рис. 8.16, которая в упрощенном виде изображается как транзистор Шоттки. Рис. 8.13 Схема транзисторного ключа с диодом Шоттки

У серий 530, 531 входы образованы многоэмиттерными транзисторами, а у серий 533, 535 – диодными логическими схемами умножения (см. диодные логические схемы). Микросхемы ТТЛ серий SN74/SN54 (74 – коммерческая, 54 – для военного применения). Аналог: SN74 – серия 155 SN74S/ SN54S – серии 530, 531 SN74LS/ SN54LS – серии 533, 555 Серия SN74F/ SN54F фирмы Faizchild (Fast–Faizchild Advanced Schottky), аналог 1531 Серия SN74ALS/SN54ALS – аналог 1533 Серия SN74AS/SN54AS S – Schottky, LS – Low power Schottky, ALS – Advanced Low Power Schottky, AS – Advanced Schottky, Advanced – усовершенствованный. Полное совпадение номеров выводов и обозначений типа для ИМС одинакового функционального ряда. В обозначении микросхем на первом месте могут стоять цифры 1, 5, 6, 7 – полупроводниковые. 2, 4, 8 – гибридные, 3 – прочие (пленочные, керамические). На втором месте цифры номера серии от 00 до 99 или от 000 до 999. Третий элемент условного обозначения – две буквы, обозначающие подгруппу и вид микросхемы, определяющие основное функциональное назначение. Четвертый элемент – число, обозначающее порядковый номер разработки ИС по функциональному признаку в данной серии. Отсчет электродов – по часовой стрелке от метки, смотреть надо на электроды.

Серийные логические ИМС. В зависимости от технологии изготовления логические ИМС делятся на серии, отличающиеся набором элементов, напряжением питания, потребляемой мощностью, динамическим параметрам и др. Наибольшее применение получили серии логических ИМС, выполненные по ТТЛ (транзисторно-транзисторная логика), ЭСЛ (эмиттерно-связанная логика) и К МОП (комплементарная МОП логика) технологиям. Каждая из перечисленных технологий совершенствовалась, поэтому в каждой серии ИМС имеются подсерии, отличающиеся по параметрам. Первым разработчиком ИМС по технологии ТТЛ является фирма Texas

Серии логических ИМС ТТЛ Таблица 8.1

Обозначения: L (low) — маломощная серия. Н (high) — быстродействующая серия, LS (low, Shotty) — маломощная с диодами Шотки, S (Shottky) — с диодами Шотки, ALS — усовершенствованная с диодами Шотки, F (fast) — сверхбыстродействующая.

Основные параметры ИМС ТТЛ различных серий приведены в табл.3. По сочетанию параметров наибольшее распространение получили ИМС серии SN74LS (серия 555). ИМС этой серии работают при напряжении питания +5В±5%. Основные параметры ИМС ТТЛ Таблица 8.2

Принцип действия ЭСЛ.

Предположим, что все входы схемы (рис. 8.20) х 0, …, х n-1 подано напряжение, близкое к – U п. тогда транзисторы VT 1 … VT n будут заперты. Весь ток резистора R n+2 протекает через транзистор VT n+1, к выводу базы которого приложено опорное напряжение U оп. Этот транзистор поддерживается в активном режиме работы за счет действия глубокой последовательной отрицательной обратной связи по току. Если не учитывать обратные токи коллекторных переходов транзисторов VT 1 … VT n через резистор R n протекает только базовый ток транзистора VT n+3 выходного эмиттерного повторителя. Следовательно, напряжение на выходе близко к нулевому U у2 = - I Б VTn+3 R n – U БЭ VTn+3. (8.7) Численно это напряжение U у2 примерно равно -0,9 В. Через резистор R n+1 кроме базового тока транзистора VT n+4 протекает ток I К VTn+1, примерно равный I Э. эти токи создают на резисторе R n+1 падение напряжения, равное U Rn+1 = (I Kn+1 + I Бn+4) R n+1 = [(I Э h 21Э)/(h 21Э + 1) + I Бn+4] R n+1 ≈ I Э R n+1.

Это напряжение преобразуется выходным эмиттерным повторителем на транзисторе VT n+4 в выходное напряжение U у1, определяемое выражением U у1 ≈ - U БЭ VTn+4 - I Э R n+1. (8.8) Численно напряжение U у1 равно – 1,7 В. Если хотя бы на один из входов х 0, …, х n-1 подать напряжение, превышающее по уровню опорное U ОП (-1,3 В), соответствующий транзистор VT перейдет в активный режим работы. Его ток равен току эмиттера I Э, что приведет к смене уровней выходного напряжения U у2 = – U БЭ VTn+3 – I Э R n, U у1 ≈ - I Б VTn+4 R n+1 - U БЭ VTn+4. (8.9)

Из сказанного выше следует, что рассмотренная схема реализует по выходу у 2 операцию ИЛИ-НЕ, а по выходу у 1 – операцию ИЛИ. Резисторы R0 - Rn-1, включенные между базами транзисторов токового ключа и выводом – UП, обеспечивают запертое состояние этих транзисторов при отсутствии входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых входов ИС к выводам источника питания. Особенностью схемотехнического построения элементов ЭСЛ является использование для подключения общей шины собственно токового переключателя и выходных эмиттерных повторителей различных выводов ИС. Потребляемый ток, протекающий в этих цепях, имеет качественно различный характер. В принципе работы токового ключа заложено потребление принципиально постоянного тока, так как его работа связана с перераспределением эмиттерного тока резистора R Э (см. рис. 8.19). Эмиттерные же повторители потребляют импульсный ток. К тому же для улучшения частотных свойств сопротивление резисторов, подключаемых к выводам у1 и у2 ИС, подбираются весьма малыми (R ВНЕШ=75…100 Ом). поэтому совместное питание этих цепей из-за малой величины логического перепада может приводить к ложному срабатыванию соседних элементов, т.е. к появлению сбоев при обработке информации (внутренних помех). Разделение цепей питания позволяет устранить этот недостаток. Раздельное питание токовых ключей и выходных эмиттерных повторителей позволяет дополнительно решить задачу снижения мощности, рассеиваемой в реальной аппаратуре. Так как выходное напряжение лежит в диапазоне -0,9…-1,7 В, то для питания внешних резисторов может быть использовано напряжение, не превышающее 2 В. Такое решение при малых значениях сопротивления R ВНЕШ позволяет значительно уменьшить бесполезные потери мощности. Рассмотренные функциональные возможности БЛЭ ЭСЛ могут быть существенно расширены простыми схемотехническими приемами. Вот два из них: совместное включение выходов нескольких элементов на общую нагрузку; многоярусное включение переключателей тока. Первый прием использует свойство эмиттерных повторителей поддерживать высокий уровень выходного напряжения, если хотя бы один из параллельно соединенных транзисторов включен (находится в активном режиме, рис. 8.16).

Рис. 8.16. Совместное включение выходов нескольких ЛЭ ЭСЛ

Логические операции, реализуемые при объединении выходов пары двухвходовых элементов, работающих с переменными х 1, х 0, у 1, у 0, иллюстрируются в табл. 8.3.

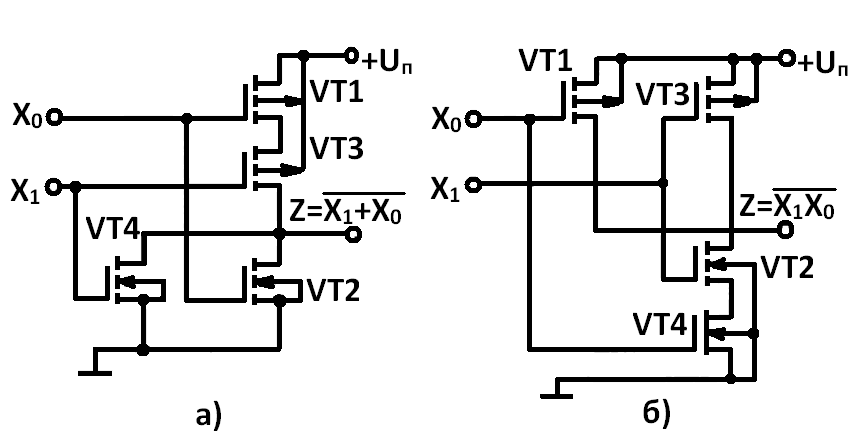

Схемотехника БЛЭ КМОП-типа

Увеличение быстродействия ИС МДП требует увеличения токов перезаряда емкостей нагрузки. Однако это ограничивается ростом потребляемой мощности и увеличением нестабильности выходных логических уровней. Преодолеть указанное противоречие можно либо технологическим путем, создавая транзисторы с меньшей входной емкостью, либо схемотехническим путем, применяя схему ключа на транзисторах с каналами различного типа (комплементарные транзисторы). Такие ключи позволяют, с одной стороны, значительно увеличить токи перезаряда емкости нагрузки, а с другой – максимально уменьшить мощность, рассеиваемую на нагрузке. Как выяснилось, ключ на комплементарных нагрузках при правильном выборе параметров входящих в него элементов в статическом режиме работы практически не потребляют энергии от источника постоянного тока. Потребляемая ЛЭ мощность в статическом режиме тождественно равна мощности, отдаваемой им в нагрузку. А так как нагрузкой элемента являются входные цепи аналогичных элементов, носящие чисто емкостной характер, то мощность, отбираемая от источника питания, расходуется только в динамическом режиме на перезаряд этой емкости, т.е. имеет минимально возможное значение. На рис. 8.19 приведена принципиальная электрическая схема транзисторного ключа, используемого в ИС КМОП.

Рис. 8.19 Принципиальная электрическая схема транзисторного ключа ИС КМОП

Она может быть разбита на три части: входной диодно-резистивный ограничитель напряжения; собственно ключ на КМОП-транзисторах; выходная диодная цепь. Входное сопротивление транзисторов, используемых в схеме ключа, достигает значения 1012 Ом. При толщине изоляции между затвором и полупроводником (слой окисла кремния) порядка 50…70 мкм его собственное пробивное напряжения составляет порядка 150…200В. Это предполагает введение в элемент специальной схемы защиты от статического электричества, которое может попасть на его вход в процессе хранения или монтажа. Роль этой схемы выполняет диодно-резистивный ограничитель на элементах VD 1, VD 2, VD 3 и R 1. Данная схема ограничивает напряжение на входе транзисторного ключа в диапазоне от – 0,7 В до U П + 0,7 В. Элементы выходной диодной цепи (VD 4, VD 5, VD 6) образованы соответствующими областями самого транзисторного ключа ис точки зрения его работы не являются обязательными. Наличие этих диодов накладывает дополнительные ограничения на использование элемента. Всегда должно выполняться неравенство | U вх – U вых|< U П. В противном случае диоды входного ограничителя и выходной цепи могут открываться, закорачивая цепь питания элемента. Последнее обстоятельство может служить причиной пробоя ЛЭ. Поэтому напряжение питания на КМОП-схемы должно всегда подаваться до включения и сниматься после отключения входного информационного сигнала. Схемотехнически БЛЭ КМОП-типа повторяет схемы nМОП- и pМОП-типов. Отличие состоит в том, что всегда используются пары транзисторов. При этом для реализации заданной логической функции транзисторы с каналом n -типа включаются последовательно, то парные им транзисторы p -типа включаются параллельно и наоборот. В качестве примера на рис. 8.20 приведены принципиальные электрические схемы, реализующие логические операции 2И-НЕ и 2ИЛИ-НЕ. Для упрощения на приведенных схемах не показаны элементы входных и выходных цепей ключа.

Рис. 8.20 Принципиальные электрические схемы БЛЭ КМОП-типа, реализующие функции 2И-НЕ (а) и 2ИЛИ-НЕ (б)

К особенностям схем БЛЭ следует также отнести отсутствие дополнительного нагрузочного резистора. Его роль выполняет один из транзисторов ключа. Анализ схемы позволяет сделать важный практический вывод о том, что аналогично БЛЭ ТТЛ для БЛЭ КМОП параллельное включение нескольких их выходов запрещено. Следует также заметить, что КМОП-элементы обладают высокой помехоустойчивостью – до 40% от напряжения питания. Достоинствами ИМС КМОП являются малая потребляемая мощность и высокая помехозащищенность в сочетании с высоким быстродействием и нагрузочной способностью. Питание таких ИМС производится от источника напряжения +5...+15В. Разработка первых ИМС КМОП серии CD4000 была выполнена фирмой

Серии логических ИМС КМОП Таблица 8.5

По сравнению с ИМС ТТЛ микросхемы КМОП имеют следующие достоинства: • малая потребляемая мощность в диапазоне частот до 2 МГц (мощность в • большой диапазон напряжений питания (от 3 до 15 В); • очень высокое входное сопротивление (больше 1 МОм); • большая нагрузочная способность (коэффициент разветвления больше 50). К недостаткам ИМС КМОП относятся: · большие времена задержки (до 100 нс); · повышенное выходное сопротивление (до 1 кОм); · значительный разброс всех параметров.

Уровни выходных сигналов зависят от напряжения питания. Уровень логической «1» равен примерно 0,8 Епит, а уровень логического «0» - от 0,3 до 2,5 В. Основные характеристики различных серий ИМС КМОП приведены в табл.8.6. Совершенствование технологии КМОП привело в настоящее время к тому, что характеристики наиболее быстродействующих ИМС КМОП серии 54НС практически сравнялись с характеристиками ИМС ТТЛ SN74LS.

ЛОГИЧЕСКИЕ СХЕМЫ 8.1 Основные определения Электронные схемы, построенные только на логике, называют комбинационными. Выход или выходы зависят только от комбинации переменных на входах. В отличие от них схемы, содержащие элементы памяти (например, триггеры), называют последовательностными. Последовательностные, так как выход (выходы) зависят не только от комбинации переменных, но и от состояния элементов памяти (последовательности записи в них).

Выделяют три основных вида логических элементов: 1. Выполняют операцию сложения (сумматор). Дизъюнкция. Логическое «ИЛИ».

2 Выполняют операцию умножения. Конъюнкция. Логическое «И».

3 Выполняют отрицание. Логическое «НЕ».

Логические элементы, реализующие эти операции, называют простейшими, а те, которые содержат несколько простейших, называют комбинированными.

Способы представления логических переменных электрическими сигналами

Значениям логических функций и аргументов в электрических схемах могут быть поставлены в соответствие различные характеристики токов или напряжений. Это могут быть как некоторые установившиеся значения, так и параметры импульсов. При потенциальном способе представления значения логических «1» и «0» ставят в соответствие два различных уровня тока или напряжения. В зависимости от того, какой именно из этих уровней конкретноставят в соответствие значениям 0 и 1, различают положительную и отрицательную логики. В положительной логике значению логической «1» ставят в соответствие большее, значению лог. «0» - меньшее значение тока или напряжения. В отрицательной логике наоборот – большим значениям электрического сигнала соответствует значения лог. «0», а меньшим значениям – значения лог. «1». Это определение справедливо для любой полярности используемого напряжения или при любых направлениях протекания токов.

Рис.8.1 Потенциальный способ представления лог. «0» и «1»: а – положительная логика; б – отрицательная логика.

Из рис. 8.1 видно, что при положительной логике и условии U вых ≥ 0 значению лог. «1» соответствует большее по абсолютному значению напряжение, в то время как при U вых < 0 большее абсолютное напряжение соответствует значению лог. «0». Однако с учетом знака уровни, показанные на рис. 8.1 (а,б) полностью соответствуют данному выше определению типов логики. Следует отметит, что если некоторое логическое устройство относительно положительной логики реализует операцию И, то относительно отрицательной логики это будет операция ИЛИ и наоборот. При импульсном способе представления лог. «1», например, может быть поставлен в соответствие сам факт наличия импульса или его положительный перепад, а значению лог. «0» - отсутствие импульса или его отрицательный перепад. Потенциальный способ представления информации позволяет определить значение логической переменной в произвольный момент времен. При использовании импульсного способа это может быть осуществлено в строго определенные фиксированные (дискретные) моменты времени. Это означает. Что при импульсном способе возможен только синхронный съем информации, а

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2021-04-13; просмотров: 202; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.128.173.32 (0.17 с.) |

. На выходе выделяется результат деления E0 между R1 и R2, который называется высоким уровнем. В том случае, когда на одном любом из входов низкий уровень, образованный такой же, другой диодной схемой, образуется цепь, к примеру,

. На выходе выделяется результат деления E0 между R1 и R2, который называется высоким уровнем. В том случае, когда на одном любом из входов низкий уровень, образованный такой же, другой диодной схемой, образуется цепь, к примеру,  выход предыдущей логической схемы

выход предыдущей логической схемы  . Следовательно, на выходе F выделяется в сущности падение напряжения на VD1 и к нему добавляется падение напряжения на внутреннем сопротивлении такой же, но другой логической схемы, т. е. низкий уровень “0”, удовлетворяется операция логического умножения.

. Следовательно, на выходе F выделяется в сущности падение напряжения на VD1 и к нему добавляется падение напряжения на внутреннем сопротивлении такой же, но другой логической схемы, т. е. низкий уровень “0”, удовлетворяется операция логического умножения.

Повысить быстродействие элемента. Нагрузка логики, как правило носит емкостной характер и применение двухтактного выходного каскада позволяет увеличить ток перезаряда емкости;

Повысить быстродействие элемента. Нагрузка логики, как правило носит емкостной характер и применение двухтактного выходного каскада позволяет увеличить ток перезаряда емкости;