Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Зарезервированные идентификаторыСодержание книги

Поиск на нашем сайте

Введение Общие положения AHDL (язык описания аппаратуры фирмы Altera) является высокоуровневым, модульным языком, полностью интегрированным в систему MAX+PLUS II. Он особенно хорошо подходит для проектирования сложной комбинационной логики, шин, конечных автоматов, таблиц истинности и параметрической логики. Вы можете использовать текстовой редактор системы MAX+PLUS II или любой другой для создания текстовых файлов проектов (AHDL Text Design Files (. tdf)). Затем Вы можете откомпилировать TDF файлы для получения выходных файлов, пригодных для последующего моделирования, временного анализа и программирования устройства. Кроме того компилятор системы MAX+PLUS II может создавать текстовые файлы экспортирования (AHDL Text Design Export Files (. tdx)) и текстовые выходные файлы (Text Design Output Files (. tdo)), которые можно сохранить как TDF файлы и повторно использовать в качестве файлов проекта. Как работает AHDL? Операторы и элементы AHDL являются мощным, многогранным и легким в использовании средством. Вы можете создавать весь иерархический проект с помощью AHDL или смешивать TDF файлы с другими типами файлов в один проект. Хотя Вы можете воспользоваться любым текстовым редактором для создания TDF файлов, но только текстовой редактор системы MAX+PLUS II дает Вам возможность воспользоваться его преимуществами, когда Вы вводите, компилируете и отлаживаете Ваш AHDL проект. AHDL проект легко вставить в иерархию проекта. В текстовом редакторе Вы можете автоматически создавать символ, представляющий TDF файл и вводить его в графический файл проекта (Graphic Design File (. gdf)). Аналогичным образом Вы можете объединять заказные функции и свыше 300 мегафункций и макрофункций, поставляемых Альтерой, включая функции библиотеки параметрических модулей (LPM), в любой TDF файл. Вы можете использовать команды меню Assign или Assignment & Configuration File (.acf) для создания ресурса и выбора устройства. Вы можете также проверить синтаксис и выполнить полную компиляцию для отладки и прогона Вашего проекта. Любые появляющиеся ошибки автоматически локализуются процессором сообщений (Message Processor) и выделяются в окне текстового редактора. Элементы языка AHDL Зарезервированные слова Зарезервированные ключевые слова используются для управления операторами AHDL, а также для предопределенных констант GND и VCC. Зарезервированные ключевые слова отличаются от зарезервированных идентификаторов тем, что ключевые слова можно использовать как символьные имена при заключении их в одиночные кавычки ('), в то время как зарезервированные идентификаторы нельзя. Как те так и другие можно свободно использовать в комментариях. Altera рекомендует вводить все ключевые слова с заглавных букв для удобства чтения. Для получения контекстно-зависимой помощи по ключевому слову сначала убедитесь, что TDF файл сохранен с расширением.tdf. Затем откройте файл в окне текстового редактора и нажмите Shift+F1 и щелкните кнопкой 1 на нем или выберите кнопку контекстно-зависимой помощи на панели инструментов. Ниже приведен список всех зарезервированных ключевых слов. Таблица 1. Зарезервированные ключевые слова языка AHDL

Символы Символы ниже имеют в языке AHDL предопределенные значения. Этот список включает символы, которые используются в качестве операторов и компараторов в булевых выражениях и как операторы в арифметических выражениях. Таблица 3. Символы языка AHDL

Шины Символьные имена и порты одного и того же типа можно объявить и использовать как шины в булевых выражениях и уравнениях. Шина, которая может содержать до 256 членов (или битов), рассматривается как коллекция узлов и действует как одно целое. Одиночные узлы и константы GND и VCC можно дублировать для создания шин. Способы объявления шин Шины можно объявить с помощью следующих трех способов: 1. Имя шины состоит из символьного имени или имени порта, за которым следует указание поддиапазона, заключенного в скобки, т.е. a[4..1]. Имя вместе с самым длинным числом в диапазоне может содержать до 32 символов. Например, Имя q[MAX..0] правильно, если константа MAX была описана выше в операторе Constant. После определения шины скобки [] являются коротким способом описания всего диапазона. Например, a [4..1] можно указать как a[]. b [6..0][3..2] можно указать как b[][]. 2. Имя шины состоит из символьного имени или имени порта, за которым следует указание поддиапазонов, заключенных в скобки, т.е. d[6..0][2..0]. Имя вместе с самым длинным числом в диапазоне может содержать до 32 символов. К индивидуальному узлу в шине можно обратиться как name[y][z] или namey_z, где y и z числа в диапазоне шины. 3. Последовательное имя шины состоит из списка символьных имен, портов или чисел, разделенных запятыми и заключенных в скобки, например, (a, b, c). Эта нотация полезна для определения имен портов. Например, Входные порты переменной reg типа DFF можно записать как reg.(d, clk, clrn, prn).

Ниже приведены две совокупности примеров, демонстрирующие две шины, описанные с помощью различной нотации:

b[5..0] (b5, b4, b3, b2, b1, b0) b[]

b[log2(256)..1+2-1] b[2^8..3 mod 1] b[2*8..8 div 2] Числа в AHDL Вы можете использовать десятичные, двоичные, восьмеричные и шестнадцатеричные числа в любых сочетаниях. Синтаксис для каждого основания показывается ниже.

Основание:Значения: Десятичное <последовательность цифр от 0 до 9> Двоичное B"<последовательность 0-ей, 1-ц и X-ов>" (где X = "безразличное состояние") Восьмеричное O"<последовательность цифр от 0 до 7>" или Q"< последовательность цифр от 0 до 7>" Шестнадцатеричное X"< последовательность цифр от 0 до 9, A до F>" H"< последовательность цифр от 0 до 9, A до F >" К числам применяются следующие правила: 1. Компилятор MAX+PLUS II всегда интерпретирует числа в булевых выражениях как группы двоичных цифр; числа в диапазонах шин как десятичные значения. 2. Числа нельзя присваивать одиночным узлам в булевых уравнениях. Вместо этого используйте VCC и GND. Арифметические выражения Арифметические выражения можно использовать для определения оцениваемых функций в операторах Define, констант в операторах Constant, значений параметров в операторах Parameters и в качестве ограничителей диапазонов шин. Пример. Диапазон, определенный с помощью арифметического выражения: SUBDESIGN foo ( a[4..2+1-3+8]: INPUT; )

Константа, определенная с помощью арифметического выражения:

CONSTANT foo = 1 + 2 DIV 3 + LOG2(256);

Оцениваемая функция, определенная с помощью арифметического выражения:

DEFINE MIN(a,b) = ((a < b)? a: b);

Арифметические операторы и компараторы используются в этих выражениях для выполнения основных арифметических и сравнительных операций с числами в них. В арифметических выражениях используются следующие операторы и компараторы. Таблица 4. Арифметические операторы языка AHDL

Ко всем арифметическим выражениям применяются следующие правила: 1. Арифметические выражения должны давать не отрицательные числа. 2. Когда результат LOG2 не целый, он автоматически округляется до следующего целого. Например, LOG2(257) = 9.

Арифметические операторы, поддерживаемые в арифметических выражениях, являются надмножеством арифметических операторов, поддерживаемых в булевых выражениях, которые описываются в 2.9.2. Логические выражения Логические выражения состоят из операндов, разделенных логическими и арифметическими операторами и компараторами и дополнительно сгруппированы с помощью круглых скобок. Выражения используются в булевых уравнениях также как и в других операторах таких как Case и If Then. Логическое выражение может быть одним из следующих: 1. Операнд Например, a, b[5..1], 7, VCC

2. Подставляемая ссылка на логическую функцию Например, out[15..0] = 16dmux(q[3..0]);

3. Префиксный оператор (! или -), применяемый к логическому выражению Например,!c

4. Два логических выражения, разделенных бинарным оператором Например, d1 $ d3

5. Логическое выражение, заключенное в круглые скобки Например, (!foo & bar) Вы можете именовать логические операторы и компараторы в файлах AHDL для облегчения ввода присваиваний ресурсов и для интерпретации раздела Equations в файле отчета. За дополнительной информацией обратитесь к 4.9.2 Арифметические операторы Арифметические операторы используются для арифметических операций сложения и вычитания над числами и шинами в булевых выражениях. В них используются следующие операторы. Таблица 6. Операторы сложения и вычитания языка AHDL

К бинарным операторам применимы следующие правила: · Операции выполняются между двумя операндами, которые должны быть шинами или числами. · Если оба операнда - шины, то они должны иметь один размер. · Если оба операнда числа, более короткое число расширяется до размеров другого операнда. · Если один оператор - число, а другой группа узлов, то число усекается или расширяется для согласования размеров операндов. Если отбрасываются любые значимые биты, то компилятор MAX+PLUS II выдает сообщение об ошибке.

ÞКогда Вы складываете две шины вместе с правой стороны булева уравнения с помощью оператора +, Вы можете поместить 0 с левой стороны группы для расширения ширины шины. Этот метод обеспечивает добавление дополнительного бита данных с левой стороны уравнения, который можно использовать как сигнал выходного переноса. Например, шины count[7..0] и delta[7..0] дополняются нулями для обеспечения информацией сигнала cout:

(cout, answer[7..0]) = (0, count[7..0]) + (0, delta[7..0]) Компараторы Для сравнения одиночных узлов или шин используются два типа компараторов: логические и арифметические. В булевых выражениях можно использовать следующие компараторы. Таблица 7. Компараторы одиночных узлов и шин

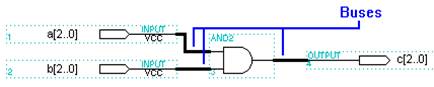

Логические компараторы могут сравнивать одиночные узлы, шины и числа без неопределенных (X) значений. При сравнении шин или чисел, шины должны иметь одинаковый размер. Компилятор MAX+PLUS II выполняет побитовое сравнение шин, возвращая VCC, когда сравнение истинно, и GND, когда сравнение ложно. Арифметические компараторы могут сравнивать только шины и числа; шины должны иметь одинаковый размер. Компилятор выполняет беззнаковое сравнение значений шин, т.е., каждая шина интерпретируется как положительное двоичное число и сравнивается с другой шиной. Примитивы MAX+PLUS II обеспечивает большое многообразие примитивных функций для разработки схем. Так как AHDL и VHDL логические операторы, порты и некоторые операторы замещают примитивы в AHDL и VHDL файлах, то примитивы являются подмножеством их, доступных для GDF файлов, как показано ниже. Примитив - один из основных функциональных блоков, применяющийся для проектирования схем с помощью программы MAX+PLUS II. Примитивы используются в графических файлах (.gdf), текстовых файлах (.tdf), и VHDL файлах (.vhd). Символы примитивов для графического редактора поставляются в директории \maxplus2\max2lib\prim, созданной во время инсталляции. Прототипы функций встроены в программу MAX+PLUS II. Массивы примитивов Массив примитивов - это примитив, который представляет несколько идентичных примитивов. Вы можете использовать примитивные массивы для создания более компактных GDF или OrCAD Schematic файлов путем ввода единственного примитива, который экстрактор списков связей компилятора переведет в несколько примитивов. Вы можете создать примитивный массив двумя способами: · Если все порты символа (pinstub) примитива соединяются с шинами, состоящими из n членов, примитив переводится в массив n индивидуальных примитивов. Каждый индивидуальный узел шины соединяется с соответствующим портом символа каждого индивидуального примитива в массиве. Например

Рис. 1. Массив примитивов (вариант 1) В этом примере примитивный массив создается при соединении трех шин A[0..2], B[0..2], и C[0..2] с двумя выводами INPUT, выводом OUTPUT и вентилем AND2. Во время обработки компилятор переводит этот примитивный массив в 6 выводов INPUT, 3 вывода OUTPUT и 3 вентиля AND2 следующим образом:

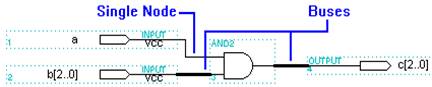

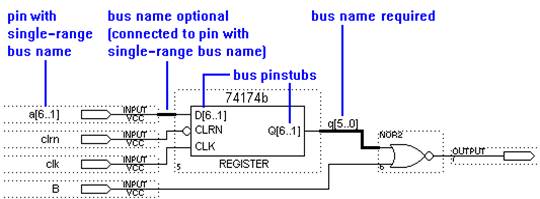

Один AND2 вентиль соединяется с узлами A0, B0, и C0. Один AND2 вентиль соединяется с узлами A1, B1, и C1. Один AND2 вентиль соединяется с узлами A2, B2, и C2. Входные выводы A0, A1, и A2 соединяются с узлами A0, A1, и A2, соответственно. Входные выводы В0, В1, и В2 соединяются с узлами В0, В1, и В2, соответственно. Выходные выводы С0, С1, и С2 соединяются с узлами С0, С1, и С2, соответственно. Примитивы выводов INPUT, INPUTC, OUTPUT, OUTPUTC, BIDIR, или BIDIRC, которым даны шинные имена переводятся в массив примитивов. Вы не можете использовать перечислимое имя шины для обозначения примитива вывода. · Если некоторые порты символа примитива соединяются с шинами с n членами, а некоторые с одиночными узлами, примитив переводится в массив n примитивов. В этом случае каждый индивидуальный узел шины соединяется с соответствующим портов символа каждого примитива в массиве, а каждый узел, который не является частью шины, соединяется с тем же самым портом символа каждого примитива. Например

Рис. 2. Массив примитивов (вариант 2) Для создания массива примитивов необходимо обозначить все используемые узлы и шины, за исключением тех случаев, где имена узлов и шин не обязательны: · Одиночный узел, который соединяется с примитивным массивом. · Шинный проводник, который соединяется с примитивным массивом, если не меньше одного сегмента сети, которая содержит этот проводник, явно обозначено перед любыми точками соединения или, если сеть соединяется с выводом с шинным именем. Например,

Рис. 3. Массив примитивов (вариант 3) Вы не можете вводить присваивания для проб и ресурсов символов примитивов, которые используются для создания примитивных массивов. Обратитесь в раздел Принципы работы с присваиваниями. Проба - уникальное имя, связанное с любым узлом, например, вход или выход примитива, мегафункции или макрофункции, которое можно использовать вместо полного иерархического имени узла в любом месте MAX+PLUS II. Таким образом пробное имя обеспечивает быструю идентификацию узла. Примитивы буферов CARRY OPNDRN CASCADE SOFT EXP TRI GLOBAL (SCLK) WIRE (только GDF) LCELL (MCELL) Примитивы триггеров и защелок DFF SRFF DFFE SRFFE JKFF TFF JKFFE TFFE LATCH Примитивы/Порты входов и выходов BIDIR или INOUT BIDIRC (только GDF) INPUT или IN INPUTC (только GDF) OUTPUT или OUT OUTPUTC(толькоGDF) Логические примитивы AND NOR BAND (только GDF) NOT BNAND (только GDF) OR BNOR (только GDF) VCC (только GDF) BOR (только GDF) XNOR GND (только GDF) XOR NAND Другие примитивы (только GDF) CONSTANT PARAM Title Block Прототипы функций для примитивов в TDF файлах не нужны. Однако Вы можете переопределить порядок вызова входов примитива, вводя оператор Function Prototype в Ваш TDF. Макрофункции MAX+PLUS II предлагает свыше 300 макрофункций. Имена шинных макрофункций оканчиваются на букву В. Они функционально идентичны с соответствующими не шинными макрофункциями, но имеют сгруппированные входные и/или выходные выводы. Для просмотра схемы или AHDL файла содержащего макрофункцию, укажите символ макрофункции в графическом редакторе или имя макрофункции в текстовом редакторе и выберите Hierarchy Down (меню File). Категории макрофункций: Сумматоры Триггеры-защелки АЛУ Умножители Буферы Мультиплексоры Компараторы Генераторы четности Конвертеры Быстрые умножители Счетчики Регистры Декодеры Сдвиговые регистры Цифровые Регистры хранения фильтры EDAC SSI функции Шифраторы Элементы ввода/вывода Делители частоты Порты Порт - это вход или выход логической функции. Порт может находится в двух местах: · Порт, который является входом или выходом текущего файла, объявляется в разделе Subdesign. · Порт, который является входом или выходом экземпляра примитива или файла разработки более низкого уровня, используется в разделе Logic. Порты текущего файла Порт, который является входом или выходом текущего файла объявляется в следующем формате в разделе Subdesign: <имя порта>: <тип порта> [ = <значение по умолчанию> ] 2.11.1. Типы портов: Доступны следующие типы портов:

INPUT MACHINE INPUT OUTPUT MACHINE OUTPUT BIDIR

Когда текстовой файл проекта является старшим в иерархии, имя порта синонимично с именем вывода. Дополнительное значение порта по умолчанию, которое может быть или VCC или GND, можно определить для типов портов INPUT и BIDIR. Это значение используется только если слева порт не подсоединен, когда экземпляр TDF применяется в файле разработки более высокого уровня. Например: SUBDESIGN top ( foo, bar, clk1, clk2, c[4..0][6..0]: INPUT = VCC; a0, a1, a2, a3, a4: OUTPUT; b[7..0]: BIDIR; )

Вы можете импортировать и экспортировать конечные автоматы между TDF и другими файлами разработки, описывая входы и выходы как MACHINE INPUT или MACHINE OUTPUT в разделе Subdesign. Прототип функции, который представляет файл, должен указывать, какие порты принадлежат конечному автомату. MACHINE INPUT и MACHINE OUTPUT можно использовать только в файлах более низкого уровня в иерархии проекта. Порты экземпляров Порт, который является входом или выходом экземпляра логической функции присоединяется в разделе Logic. Для соединения логической функции с другими частями TDF, Вы вставляете экземпляр функции с помощью подставляемой ссылки, объявления Instance или конечного автомата с помощью State Machine и затем используете порты функции в разделе Logic. Если Вы используете подставляемую ссылку с присваиванием по положению порта для создания экземпляра логической функции, важен порядок портов, а не имена. Порядок портов определяется в прототипе функции. Если Вы используете объявление Instance или подставляемую ссылку со связью по имени для создания экземпляра логической функции, важны имена портов, а не их порядок. В следующем примере D триггер объявляется как переменная reg в разделе Variable, а затем используется в разделе Logic:

VARIABLE reg: DFF; BEGIN reg.clk = clk reg.d = d out = reg.q END;

Имена портов используются в следующем формате в разделе Logic:

<имя экземпляра>.<имя порта>

<имя экземпляра> - это имя функции, данное пользователем. <имя порта> идентично с именем порта, который объявляется как вход или выход файла в разделе Subdesign TDF файла более низкого уровня или имя вывода в файле разработки другого типа. <имя порта> синонимично с именем порта символа (pinstub), который представляет экземпляр файла разработки в GDF. Все функции, поставляемые Altera, имеют предопределенные имена портов (pinstub), которые показываются в прототипе функции. Наиболее используемые имена портов примитивов показаны в следующей таблице:

Имя порта Описание

.q Выход триггера или защелки .d Вход данных триггера или защелки .t Вход T триггера .j J вход JK триггера .k K вход JK триггера .s Вход установки SR триггера .r Вход очистки SR триггера .clk Тактовый вход триггера .ena Вход разрешения тактирования триггера, разрешения фиксации защелки разрешения конечного автомата .prn Активный низкий вход предустановки триггера .clrn Активный низкий вход очистки триггера .reset Активный высокий вход сброса конечного автомата .oe Вход разрешения выхода TRI примитива .in Первичный вход CARRY, CASCADE, EXP, TRI, OPNDRN, SOFT, GLOBAL, и LCELL примитивов .out Выход TRI, OPNDRN, SOFT, GLOBAL, и LCELL примитивов Общая структура Текстовый файл проекта на языке AHDL должен содержать, как минимум, два раздела: Subdesign и Logic. Все остальные разделы и операторы являются необязательными. В предлагаемом к ознакомлению разделе ‘Структура проекта’ информация об операторах и разделах языка AHDL дается в том порядке, в котором они следуют в текстовом файле проекта (TDF - Text Design File). Разделы и операторы языка AHDL описываются в том порядке, в котором они следуют в текстовом файле проекта (TDF - Text Design File). 1. Оператор Title 2. Оператор Parameters 3. Оператор Include 4. Оператор Constant 5. Оператор Define 6. Оператор Function Prototype 7. Оператор Options 8. Оператор Assert Раздел Subdesign 10. Раздел Variable 10.1. Раздел Logic 11.1. Задание исходных значений (Defaults Statment) Оператор Defaults позволяет определять значения по умолчанию, применяемые в таблицах истинности, а также в операторах If Then и Case. Поскольку активно- высокие сигналы автоматически имеют значения по умолчанию GND, то оператор Default необходим лишь в случае использования активно-низких сигналов.

ÞНе следует путать значения по умолчанию, присваиваемые переменным со значениями по умолчанию, присваиваемыми портам в разделе Subdesign. Следующий пример демонстрирует использование оператора Defaults:

BEGIN DEFAULTS a = VCC; END DEFAULTS;

IF y & z THEN a = GND; % a активный низкий % END IF; END;

Оператор Defaults имеет следующие характеристики: ¨ Значения по умолчанию заключаются в ключевые слова DEFAULTS и END DEFAULTS. Оператор заканчивается символом (;). ¨ Тело оператора Defaults состоит из одного или более логических выражений, присваиваемых константам или переменным. В примере, показанном выше, значение по умолчанию VCC присваивается переменной a. ¨ Каждое выражение заканчивается символом (;). ¨ Оператор Default активизируется в том случае, когда какая-либо переменная, включенная в список оператора Default в каком-либо из операторов, оказывается неопределенной. В примере, показанном выше, переменная a оказывается неопределенной, если y и z имеют значения логического нуля; таким образом активизируется выражение (a = VCC) в операторе Default. При использовании оператора Default необходимо соблюдать следующие правила:

¨ В разделе Logic допускается использовать не более одного оператора Default и кроме того при его использовании он должен располагаться сразу за ключевым словом BEGIN. ¨ Если в операторе Default в отношении одной и той же переменной производятся многократные присваивания, то все присваивания за исключением последней игнорируются. ¨ Оператор Default не может использоваться для присваивания значения X (безразлично) переменным. ¨ Многократные присваивания значений узлу, имеющему тип NODE, объединяются в соответствии с функцией логическое ИЛИ, за исключением того случая, когда значением по умолчанию для этой переменной является VCC. Следующий пример текстового файла проекта (TDF) иллюстрирует значения по умолчанию для двух переменных: a с значением по умолчанию GND и bn с значением по умолчанию VCC:

BEGIN DEFAULTS a = GND; bn = VCC; END DEFAULTS;

IF c1 THEN a = a1; bn = b1n; END IF;

IF c2 THEN a = a2; bn = b2n; END IF; END;

Этот пример эквивалентен следующему выражению: a = c1 & a1 # c2 & a2; bn = (!c1 # b1n) & (!c2 # b2n);

¨ Переменные, имеющие активно низкий уровень и участвующие в многократных присваиваниях, должны иметь значение по умолчанию VCC. В следующем примере reg[].clrn имеет значение по умолчанию VCC:

SUBDESIGN 5bcount ( d[5..1]: INPUT; clk: INPUT; clr: INPUT; sys_reset: INPUT; enable: INPUT; load: INPUT; q[5..1]: OUTPUT; ) VARIABLE reg[5..1]: DFF; BEGIN DEFAULTS reg[].clrn = VCC; END DEFAULTS;

reg[].clk = clk; q[] = reg[];

IF sys_reset # clr THEN reg[].clrn = GND; END IF;

!reg[].prn = (load & d[]) &!clr; !reg[].clrn = load &!d[]; reg[] = reg[] + (0, enable); END; 3.12.2. Булевские выражения (Boolean Equations) Булевские выражения используются в разделе Logic текстового файла проекта на языке AHDL для представления соединений узлов, входных и выходных потоков сигналов через входные и выходные выводы, примитивы, макро- и мегафункции и конечные автоматы. Следующий пример демонстрирует сложное булевское выражение:

a[] = ((c[] & -B"001101") + e[6..1]) # (p, q, r, s, t, v);

Левая часть выражения может быть символическим именем, именем порта или именем группы. Для инвертирования выражения в левой части выражения можно пользоваться операцией NOT (!). Правая часть равенства представлена булевским выражением, вычисляемым в порядке, описанном в разделе “Приоритеты булевских операторов и операций отношения”. Символ эквивалентности (=) используется в булевских выражениях для индикации того, что результат булевского выражения, представленного в правой части, является источником сигнала для символического объекта или группы в левой части. Символ (=) отличается от символа (==), используемого как компаратор. В примере, показанном выше, булевское выражение в правой части равенства вычисляется в соответствии со следующими правилами:

1. Двоичное число B”001101” меняет знак и принимает вид B”110011”. Унарная операция (-) имеет наивысший приоритет. 2. B”110011” объединяется по И с группой c[]. Эта операция имеет второй уровень приоритета, потому что она заключена в круглые скобки. 3. Результат групповой операции, проведенной на втором шаге, прибавляется к группе e[6..1]. 4. Результат, полученный на третьем шаге, объединяется по ИЛИ с группой (p, q, r, s, t, v). Это выражение имеет наименьший уровень приоритета.

Результат операции присваивается группе a[ ].

Для корректного выполнения операций, показанных выше, необходимо, чтобы количество бит в группе в левой части выражения было равно или делилось нацело на число бит в группе в правой части выражения. Биты в левой части выражения отображаются на соответствующие биты в правой части выражения по порядку.

В отношении булевских выражений используются следующие правила:

¨ Множественные присваивания, осуществляемые в отношении переменной объединяются в соответствии с монтажным ИЛИ (#), исключая тот случай, когда значением по умолчанию для этой переменной является VCC. ¨ Узлы в левой части булевского выражения однозначно соответствуют узлам в правой части. ¨ Если значение одиночного узла, VCC или GND присваиваются группе, то значение узла или константы копируется до размерности группы. Например, (a, b) = e эквивалентно a = e и b = e. ¨ Если и левая и правая части выражения представляют собой группы одинакового размера, то каждый член группы, расположенной в правой части, соответствует тому члену группы в левой части, который расположен на той же позиции.Например, (a, b) = (c, d) эквивалентно a = c и b = d.

ÞПри сложении двух групп в правой части булевского выражения с использованием операции (+) можно добавить символ “0” слева каждой группы для знакового расширения. Этот метод может быть использован для получения дополнительного бита сигнала переноса в группе, расположенной в левой части выражения. В следующем примере группы count[7..0] и delta[7..0] представлены в знакорасширенном формате для получения значения бита переноса, обозначенного символическим именем cout в левой части выражения:

(cout, answer[7..0]) = (0, count[7..0]) + (0, delta[7..0])

¨ Если в левой и правой частях булевского выражения расположены группы разных размерностей, то количество бит в группе слева должно быть равно или делиться нацело на количество бит в правой части выражения. Биты в левой части выражения отображаются на биты в правой части выражения по порядку. Следующая запись является корректной: a[4..1] = b[2..1] В данном выражении биты отображаются в следующем порядке: a4 = b2 a3 = b1 a2 = b2 a1 = b1 ¨ Группа узлов или чисел не может быть присвоена одиночному узлу. ¨ Если число в правой части выражения присваивается группе, расположенной в левой части выражения, то число усекается или расширяется путем распространения знака до соответствия размеру группы в левой части. Если при этом происходит усечение значащих битов, то компилятор выдает сообщение об ошибке. Каждый член в правой части выражения присваивается соответствующему члену в левой части выражения по порядку. Например, (a, b) = 1 эквивалентно a = 0; b =1; ¨ Запятые могут использоваться для резервирования места под неупомянутые элементы группы в булевских выражениях Следующий пример демонстрирует использование запятых для резервирования места под отсутствующие элементы группы (a, b, c, d): (a,, c,) = B"1011"; В данном примере элементам a и c присваивается значение “1”. ¨ Каждое выражение заканчивается символом (;). Применение языка AHDL В данном разделе описывается как разрабатывать проект на AHDL и предлагаются советы по созданию успешных проектов. Использование шаблонов AHDL Текстовой редактор позволяет Вам вставить шаблон любого из операторов или разделов AHDL в текущий файл. Шаблоны AHDL - это простой способ ввода синтаксических конструкций языка AHDL, увеличивающий скоро

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 352; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.5 (0.016 с.) |