Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

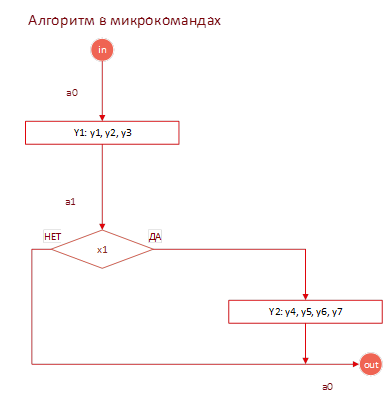

Определение необходимых микроопераций, микрокоманд и признаков

Y2 выполняется при условии x1: XNOR_1 = 1 (A[0] == B[i])

Описание используемых микросхем и элементов

¾ POS – смена напряжения с низкого на высокое (0 на 1) ¾ X – любое значение

Регистр имеет последовательные входы данных SR и SL. Данные на выходах появляются при перепаде с 0 на 1 тактового импульса на входе CLK. Для этого подадим на этот вход сигнал с генератора тактовых импульсов Clock, который вырабатывает последовательность прямоугольных импульсов, чтобы с каждым тактовым импульсом можно было наблюдать изменение состояния регистров. С заданной частотой генератор выдает уровень логической единицы, а затем нуля. Вход CLR’ – сброс схемы в ноль. Для записи параллельного кода устанавливают S1=S0=1. Сигнал S1=0 осуществляет сдвиг влево, а S0=0 осуществляют сдвиг вправо. Для записи последовательного кода используют один из двух входов: SR или SL (SR – сдвиг кода вправо, SL – сдвиг кода влево). При записи данных через вход SR устанавливают S1=0, S0=1, а при значении S1=1, S0=0 происходит сдвиг вправо. При записи данных через вход SL установление сигналов S1, S0 противоположно, а сдвиг записанного кода будет влево.

Кодер (шифратор) 74148

Шифраторы (кодеры) используются чаще всего для преобразования десятичных чисел в двоичный или двоично-десятичный код, например, в микрокалькуляторах, в которых нажатие десятичной клавиши соответствует генерации соответствующего двоичного кода. Поскольку возможно нажатие сразу нескольких клавиш, в шифраторах используется принцип приоритета старшего разряда, т.е. при нажатии клавиш 9, 5 и 2 на выходе шифратора будет генерироваться код 1001, соответствующий цифре 9. Следует отметить, что шифраторы как отдельный класс функциональных устройств представлены в наиболее богатой ТТЛ-серии всего двумя ИМС — 74147 и 74148, причем последняя ИМС имеется и в библиотеке программы EWB.

2. Полусумматор (Half Adder – HA) Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S и C, где S — это бит суммы по модулю 2, а C — бит переноса.

|

|||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-08; просмотров: 497; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.141.24.134 (0.004 с.) |

nB

nB