Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Цифроаналоговые преобразователи. Аналого-цифровые преобразователи.

Цифроаналоговые преобразователи. При построении ЦАП широкое распространение получил принцип суммирования токов, поступающих из цепей, каждая из которых отражает состояние текущего разряда двоичного кода. Недостатки: необходимость использования резисторов с номиналами, изменяющимися в широком диапазоне от

Рисунок 22.3 – Структурная схема ЦАП с матрицей R – 2R Номиналы всех резисторов в такой схеме ограничены только двумя значениями В схеме, представленной на рисунке 22.4, ток

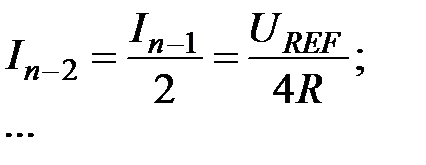

где Считая, что Принцип организации резистивной матрицы

Входное сопротивление относительно узла

Аналогично

Поскольку сопротивления цепей матрицы, подключенных к соответствующим узлам

или в общем виде Поскольку при произвольном коде

Тогда для

Из полученной формулы видно, что Аналого-цифровые преобразователи. АЦП по своей сути, реализуют принцип измерения. Это означает, что в процессе преобразования осуществляется сравнение неизвестной величины с некоторым заданным эталонным значением. Рассмотрим принципы реализации АЦП. АЦП последовательного счета. АЦП данного класса осуществляют сравнение входной аналоговой величины с суммой значений нескольких одинаковых эталонов. Момент равенства этих величин фиксируется безгистерезисным компаратором. Структура одного из вариантов такого АЦП, получившего название развертывающего, или циклического, представлена на рисунке 22.4 а.

а

б Рисунок 22.4 – Структурная схема (а) и временная диаграмма работы (б)развертывающего АЦП На вход компаратора DA1 поступают два аналоговых сигнала – входное напряжение

В исходном состоянии на входе Start схемы присутствует уровень логического нуля (рисунок 22.4 б). Данный уровень является активным длявхода Для приведения АЦП в исходное состояние необходимо счетчик DD2 нулевым сигналом Start сбросить в нуль (момент времени Из временной диаграммы очевидно, что время преобразования Недостаток развертывающего АЦП заключается в его низком быстродействии, поскольку в процессе каждого преобразования суммирование эталонов начинается с нулевого значения. Этого недостатка лишены следящие, или нециклические, АЦП. Принцип их работы основан на том, что суммирование эталонов с нулевого значения осуществляется только при первом преобразовании. В дальнейшем следящий АЦП лишь корректирует выходной код в зависимости от входного аналогового сигнала. Структурная схема следящего АЦП приведена на рисунке 22.5 а.

Особенностью этой схемы является использование реверсивного счетчика DD4. Счетные импульсы на вход счетчика подаются через стробирующие элементы И DD1 и DD2.

а

б Рисунок – 22.5 – Структурная схема (а) и временная диаграмма работы (б) следящего АЦП Если выполняется условие Пока на входе «Start» присутствует нулевой уровень сигнала на выходе ЦАП DD5 удерживается нулевой потенциал (рисунок 22.5 б). При этом выполняется условие Время преобразования

Для установки D -триггера в первоначальное единичное состояние и формирования единичного уровня сигнала Busy в него по переднему фронту сигнала Start записывается логическая единица с входа D. Эта единица будет сохраняться до тех пор, пока на выходе компаратора не сформируется нулевой потенциал, являющийся признаком завершения первого развертывающего преобразования. Этот нуль проинвертируется инвертором DD3 и, будучи уже единицей, поступит на вход R триггера и установит его в нулевое состояние. На выходе триггера сформируется нулевой уровень сигнала Busy. В дальнейшем это состояние триггера будет оставаться неизменным по причине отсутствия каких-либо воздействий, устанавливающих его в единичное состояние. Таким образом, сигнал Busy будет выполнять функцию признака завершения первого развертывающего преобразования. После подачи нулевого сигнала Start на вход схемы АЦП для приведения ее в исходное состояние единичный сигнал установки в нуль с входа R D -триггера снимется с некоторой задержкой, обусловленной временем срабатывания элементов (в порядке очередности их срабатывания) DD4, DD5, DA1 и DD3. Поэтому сигнал Start на динамический вход С D -триггера для его установки в единичное состояние необходимо подавать после того, как будет снята логическая единица со статического входа R этого триггер т.е. с некоторой задержкой по переднему фронту. Для этих целей служит схема задержки DL. Важно отметить, что скорость изменения амплитуды входного аналогового сигнала, подаваемого на следящий АЦП, не должна превышать частоты следования тактовых импульсов. В противном случае АЦП не будет успевать отслеживать изменение входного сигнала. АЦП последовательного приближения. В основе метода последовательного приближения, или, как его еще называют, поразрядного уравновешивания, лежит принцип сравнения амплитуды входного аналогового сигнала с сумой различных по значению эталонов. Число таких эталонов равно числу разрядов АЦП, а их значения пропорциональны отдельным разрядам двоичного кода. Эталон с самым большим значением напряжения соответствует старшему разряду кода, а с самым малым – младшему. Причем значение каждого следующего эталона вдвое меньше значения предыдущего. Сумма значений всех эталонов соответствует величине максимального входного напряжения АЦП. Просуммировав только те эталоны, общее значение которых совпадет с напряжением входного сигнала, на выходе АЦП установится соответствующий этим значениям двоичный код. Структурная схема АЦП последовательного приближения приведена на рисунке 22.6 а.

а

б Рисунок 22.6 – Структурная схема (а) и временная диаграмма работы (б) АЦП последовательного приближения Элементы DD2.i... DD4.i образуют так называемый регистр последовательных приближений. Преобразование начинается с выставления единичного импульса на входе Start (момент времени

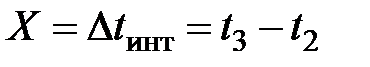

Таким образом, на входе ЦАП DD5 фиксируется код с единицей в самом старшем разряде и нулями в остальных разрядах. Передним фронтом импульса тактового генератора единичный уровень сигнала Start записывается в младший разряд Q0 последовательного регистра DD1, который, в свою очередь, открывает стробирующий элемент И DD2.0. Если значение выходного напряжения с ЦАП превышает или равняется амплитуде входного сигнала, т.е. выполняется условие Если выходное напряжение с ЦАП оказывается меньше амплитуды входного сигнала, т.е. выполняется Вторым тактовым импульсом осуществляется сдвиг единицы врегистре из разряда Q0 в разряд Q1. Сигнал Start при этом должен быть сброшен в нуль. Тогда в разряде Q0 регистра формируется логический нуль. Элемент DD2.0 закрывается, а элемент DD2.1 открывается. Триггер DD4.0 оказывается лишенным каких-либо воздействий и сохраняет сформированное значение старшего разряда двоичного кода. Логическая единица с выхода Q1 регистра подается на вход установки S триггера DD4.1 и устанавливает в единичное состояние. На входе ЦАП формируется новый код сохраненным значением старшего разряда Если Очевидно, что время преобразования Двухтактный интегрирующий АЦП. В основу метода двухтактного интегрирования положен принцип сравнения значения интеграла амплитуды входного аналогового сигнала

Двоичный код может быть получен путем заполнения интервала Упрощенная структурная схема, не раскрывающая схемы управления, представлена на рисунке 22.7 а.

а

б Рисунок 22.7 – Структурная схема (а) и временная диаграмма работы (б) двухтактного интегрирующего АЦП В исходном состоянии ключи SW1 и SW2 разомкнуты, a SW3 – замкнут. Это обеспечивает нулевое начальное напряжение на конденсаторе С и нулевое напряжение на выходе интегратора. Выполняется условие Цифровой код двухтактного интегрирующего АЦП определяется как:

Таким образом, количество подсчитанных двоичным счетчиком тактовых импульсов в период АЦП с непосредственной оценкой. В основе метода непосредств ен ной оценки лежит принцип одновременного сравнения входного напряжения со всеми квантованными уровнями. АЦП, построенные по такому принципу, называются еще параллельными. Для реализации такого принципа АЦП в своей структуре должен содержать

Рисунок 22.8 – Структурная схема АЦП с непосредственной оценкой Так как все компараторы срабатывают одновременно, то преобразование осуществляется за один такт. Преимущество параллельного АЦП заключается в его максимальном быстродействии по сравнению с АЦП других типов. Максимальная частота преобразования В настоящее время широкое распространение получили АЦП и ЦАП с последовательной передачей выходного и входного кодов соответственно. Это означает, что передаваемый из преобразователя или в преобразователь двоичный код представляется не в параллельном, а в последовательном виде, т.е. все разряды двоичного кода передаются по одному каналу поочередно путем их сдвига. Такая организация интерфейса обмена данными позволяет сократить число выводов микросхемы преобразователя. Например, существуют микросхемы АЦП и ЦАП всего с восемью выводами. В структуре таких преобразователей присутствуют регистры сдвига, заполняемые или считываемые с помощью специальных синхронизирующих передачу импульсов Clock. Разумеется, что такая организация обмена данными снижает производительность преобразователя, которая в некоторых случаях начинает определяться не собственно частотой преобразования, а скоростью передачи двоичного кода. Преобразователи с последовательной передачей кода широко используются при обработке сигналов в диапазоне звуковых частот, т.е. не превышающих десятки килогерц. Контрольные вопросы 1 Какие методы дискретизации аналоговых сигналов вам известны? 2 Какие характеристика АЦП и ЦАП на ваш взгляд определяют их точность? 3 Какими недостатками обладает структура ЦАП с резисторами 4 Опишите принцип функционирования ЦАП с резисторной матрицей R-2R. 5 Сформулируйте принцип аналого-цифрового преобразования методом последовательного счета. 6 Почему АЦП последовательного приближения обладает более высоким быстродействием по сравнению с АЦП последовательного счета? 7 АЦП каких типов следует выбирать при оцифровке аналоговых сигналов с частотами в диапазоне сотен МГц и в диапазоне единиц герц? 8 Каким преимуществом и недостатком обладает последовательный канал передачи двоичного кода в ЦАП или из АЦП? Лекция 23

|

|||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 632; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.138.122.195 (0.052 с.) |

до

до  , обладающими прецизионной точностью. Поэтому большее распространение получила схема, использующая резистивную матрицу

, обладающими прецизионной точностью. Поэтому большее распространение получила схема, использующая резистивную матрицу  (рисунок 22.3).

(рисунок 22.3).

. В схеме предусмотрены переключающие ключи на транзисторах

. В схеме предусмотрены переключающие ключи на транзисторах  и

и  в каждом разряде. Таким образом, при подаче на разрядный вход

в каждом разряде. Таким образом, при подаче на разрядный вход  логического нуля открывается транзистор

логического нуля открывается транзистор  и соответствующая цепь резисторной матрицы с резистором номиналом

и соответствующая цепь резисторной матрицы с резистором номиналом  замыкается на нулевой потенциал общего провода. Транзистор

замыкается на нулевой потенциал общего провода. Транзистор  при этом остается закрытым. Если на вход

при этом остается закрытым. Если на вход  подан потенциал логической единицы, то транзистор

подан потенциал логической единицы, то транзистор  оказывается закрытым, а транзистор

оказывается закрытым, а транзистор  , на затворе которого действует нулевой потенциал с выхода инвертора

, на затворе которого действует нулевой потенциал с выхода инвертора  – открытым. Таким образом, ток из

– открытым. Таким образом, ток из  -й цепи резистивной матрицы попадает на вход ОУ.

-й цепи резистивной матрицы попадает на вход ОУ. , присутствует всегда. Разрядными ключами

, присутствует всегда. Разрядными ключами  осуществляется коммутация этого тока либо в общий минусовой вывод источника питания, либо в цепь отрицательной обратной связи ОУ с резистором

осуществляется коммутация этого тока либо в общий минусовой вывод источника питания, либо в цепь отрицательной обратной связи ОУ с резистором  . Входное сопротивление инверсного входа ОУ, охваченного отрицательной обратной связью:

. Входное сопротивление инверсного входа ОУ, охваченного отрицательной обратной связью:

– коэффициент усиления по напряжению операционного усилителя без обратной связи.

– коэффициент усиления по напряжению операционного усилителя без обратной связи. , можно принять, что

, можно принять, что  . Тогда ток

. Тогда ток  , втекающий как в общий минусовой провод, так и в цепь обратной связи с

, втекающий как в общий минусовой провод, так и в цепь обратной связи с  можно считать одинаковым по величине в обоих случаях.

можно считать одинаковым по величине в обоих случаях. заключается в том, что входное сопротивление относительно разрядных узлов матрицы

заключается в том, что входное сопротивление относительно разрядных узлов матрицы  всегда равно

всегда равно  . Для наглядности примем, что во всех разрядах

. Для наглядности примем, что во всех разрядах  присутствуют логические нули, т.е. все цепи

присутствуют логические нули, т.е. все цепи  резисторной матрицы замкнуты на землю. Тогда входное сопротивление относительно узла

резисторной матрицы замкнуты на землю. Тогда входное сопротивление относительно узла  есть параллельное соединение двух резисторов

есть параллельное соединение двух резисторов  :

:

будет определяться из условия параллельного соединения сопротивления

будет определяться из условия параллельного соединения сопротивления  и последовательно соединенных сопротивлений

и последовательно соединенных сопротивлений  и

и  :

:

и

и  . В результате имеем, что входное сопротивление всей матрицы равно

. В результате имеем, что входное сопротивление всей матрицы равно  , а суммарный ток

, а суммарный ток

одинаковые, то ток на выходе из очередного узла будет разделяться на две одинаковые составляющие

одинаковые, то ток на выходе из очередного узла будет разделяться на две одинаковые составляющие  :

:

;

;

не все токи

не все токи  могут образовывать суммарный ток

могут образовывать суммарный ток  , втекающий в цепь обратной связи ОУ, а только те, которые коммутируются транзисторами

, втекающий в цепь обратной связи ОУ, а только те, которые коммутируются транзисторами  под управлением соответствующих разрядов

под управлением соответствующих разрядов  двоичного кода, то в общем случае для

двоичного кода, то в общем случае для  можно записать

можно записать

можно записать

можно записать

ЦАП пропорционально входному двоичному коду и не зависит от сопротивления нагрузки. Можно отметить также, что сопротивления всего с двумя номиналами

ЦАП пропорционально входному двоичному коду и не зависит от сопротивления нагрузки. Можно отметить также, что сопротивления всего с двумя номиналами  и

и  относительно легко изготовить с хорошо согласованными характеристиками, что в значительной степени определяет точность ЦАП.

относительно легко изготовить с хорошо согласованными характеристиками, что в значительной степени определяет точность ЦАП.

схемы и выходное напряжение

схемы и выходное напряжение  с ЦАП DD3 в виде эталонных квантованных уровней. Компаратор устанавливает соотношение мгновенных амплитуд этих напряжений. Если

с ЦАП DD3 в виде эталонных квантованных уровней. Компаратор устанавливает соотношение мгновенных амплитуд этих напряжений. Если  , на выходе компаратора устанавливаете уровень напряжения логической единицы; если

, на выходе компаратора устанавливаете уровень напряжения логической единицы; если  , то на выходе компаратора устанавливается напряжение логического нуля. Единичный уровень сигнала с выхода компаратора, поступая на вход стробирующего элемента И DD1, разрешает передачу на счетный вход счетчика DD2 тактовых импульсов с генератора GN. В противном случае, если на выходе компаратора логический нуль, счетные импульсы на вход счетчика не проходят, т.е. подсчет импульсов осуществляется при условии

, то на выходе компаратора устанавливается напряжение логического нуля. Единичный уровень сигнала с выхода компаратора, поступая на вход стробирующего элемента И DD1, разрешает передачу на счетный вход счетчика DD2 тактовых импульсов с генератора GN. В противном случае, если на выходе компаратора логический нуль, счетные импульсы на вход счетчика не проходят, т.е. подсчет импульсов осуществляется при условии

установки счетчика в нулевое состояние. В результате нулевой двоичный код с выхода счетчика поступает на вход ЦАП, на выходе которого устанавливается нулевое напряжение

установки счетчика в нулевое состояние. В результате нулевой двоичный код с выхода счетчика поступает на вход ЦАП, на выходе которого устанавливается нулевое напряжение  . Если входное напряжение

. Если входное напряжение  и счетные импульсы проходят на входсчетчика. При этом счетчик удерживается в нулевом состоянии нулевым значением Start. Для запуска преобразования в момент времени

и счетные импульсы проходят на входсчетчика. При этом счетчик удерживается в нулевом состоянии нулевым значением Start. Для запуска преобразования в момент времени  на вход Start подается уровень логической единицы. Начинается подсчет импульсов с тактового генератора. С каждым текущим импульсом на выходе ЦАП будет формироваться потенциал следующего квантованного уровня. Как только выходное напряжение ЦАП достигнет или превысит амплитуду входного аналогового сигнала схемы, т.е. выполнится условие

на вход Start подается уровень логической единицы. Начинается подсчет импульсов с тактового генератора. С каждым текущим импульсом на выходе ЦАП будет формироваться потенциал следующего квантованного уровня. Как только выходное напряжение ЦАП достигнет или превысит амплитуду входного аналогового сигнала схемы, т.е. выполнится условие  компаратор переключится в нулевое состояние, элемент И закроется и подсчет тактовых импульсов прекратится. На выходе счетчика зафиксируется выходной код, соответствующий величине

компаратор переключится в нулевое состояние, элемент И закроется и подсчет тактовых импульсов прекратится. На выходе счетчика зафиксируется выходной код, соответствующий величине  . На временной диаграмме этому соответствует момент времени

. На временной диаграмме этому соответствует момент времени  . Время преобразования –

. Время преобразования –  .

. ). На выходе ЦАП сформируется нулевое выходное напряжение, выполнится условие

). На выходе ЦАП сформируется нулевое выходное напряжение, выполнится условие  , под действием нулевого уровня сигнала Start на выходе счетчика будет сохраняться нулевой двоичный код. Для запуска следующего преобразования на вход Start необходимо снова подать уровень логической единицы (момент времени

, под действием нулевого уровня сигнала Start на выходе счетчика будет сохраняться нулевой двоичный код. Для запуска следующего преобразования на вход Start необходимо снова подать уровень логической единицы (момент времени  ). Процесс преобразования повторится. Как только в очередной раз выполнится условие

). Процесс преобразования повторится. Как только в очередной раз выполнится условие  (момент времени

(момент времени  ), преобразование завершится. Время преобразования в этом случае –

), преобразование завершится. Время преобразования в этом случае –  .

. и

и  различно и зависит от частоты следования тактирующих импульсов и формы входного аналогового сигнала. Поэтому для синхронизации работы АЦП с другими устройствами выход компаратора используется еще и как управляющий сигнал Busy. Этот сигнал является признаком завершения преобразования. Пока сигнал Busy имеет единичный уровень, АЦП выполняет преобразование, на выходах

различно и зависит от частоты следования тактирующих импульсов и формы входного аналогового сигнала. Поэтому для синхронизации работы АЦП с другими устройствами выход компаратора используется еще и как управляющий сигнал Busy. Этот сигнал является признаком завершения преобразования. Пока сигнал Busy имеет единичный уровень, АЦП выполняет преобразование, на выходах  , присутствуют промежуточные неверные коды. Считывание информации с этих выходов следует производить только после того, как сигнал Busy примет нулевое значение, т.е. после завершения преобразования.

, присутствуют промежуточные неверные коды. Считывание информации с этих выходов следует производить только после того, как сигнал Busy примет нулевое значение, т.е. после завершения преобразования.

, то единичным сигналом с выхода компаратора элемент DD1 пропускает счетные импульсы на вход «+1» счетчика. На вход элемента DD2 в этом случае через инвертор DD3 подается логический нуль, в результате чего на выходе DD2 также формируется логический нуль, который подается на вход «-1» счетчика. Счетчик осуществляет положительный счет. Если же выполняется условие

, то единичным сигналом с выхода компаратора элемент DD1 пропускает счетные импульсы на вход «+1» счетчика. На вход элемента DD2 в этом случае через инвертор DD3 подается логический нуль, в результате чего на выходе DD2 также формируется логический нуль, который подается на вход «-1» счетчика. Счетчик осуществляет положительный счет. Если же выполняется условие  , то закрывается элемент DD1, инвертором DD3 открывается элемент DD2, через который счетные импульсы подаются на вход «-1» счетчика, и счетчик начинает выполнять операцию отрицательного счета.

, то закрывается элемент DD1, инвертором DD3 открывается элемент DD2, через который счетные импульсы подаются на вход «-1» счетчика, и счетчик начинает выполнять операцию отрицательного счета. и счетные импульсы подаются на вход «+1» счетчика. Как только на вход Start поступает логическая единица, разрешается положительный счет (момент времени

и счетные импульсы подаются на вход «+1» счетчика. Как только на вход Start поступает логическая единица, разрешается положительный счет (момент времени  ). Счет будет продолжаться до тех пор, пока выходное напряжение с ЦАП, пропорциональное коду подсчитанных импульсов, не достигнет значения амплитуды входного аналогового сигнала (момент времени

). Счет будет продолжаться до тех пор, пока выходное напряжение с ЦАП, пропорциональное коду подсчитанных импульсов, не достигнет значения амплитуды входного аналогового сигнала (момент времени  ). При этом выполнится условие

). При этом выполнится условие  и счетчик начнет операцию отрицательного счета. Отрицательный счет будет продолжаться, пока вновь не выполнится условие

и счетчик начнет операцию отрицательного счета. Отрицательный счет будет продолжаться, пока вновь не выполнится условие  и счетчик не вернется к положительному счету. Таким образом, схема АЦП будет постоянно отслеживать амплитуду входного аналогового сигнала и пропорционально ей формировать выходной код

и счетчик не вернется к положительному счету. Таким образом, схема АЦП будет постоянно отслеживать амплитуду входного аналогового сигнала и пропорционально ей формировать выходной код  .

. обусловлено процессом только самого первого развертывающего преобразования и зависит от амплитуды входного сигнала. Для возможности синхронизации с другими устройствами в схеме следящего АЦП также предусмотрен управляющий сигнал Busy. Поскольку сигнал с выхода компаратора в зависимости от направления счета постоянно меняет свое значение с единицы на нуль, то для фиксации момента окончания первого следящего преобразования (момент времени

обусловлено процессом только самого первого развертывающего преобразования и зависит от амплитуды входного сигнала. Для возможности синхронизации с другими устройствами в схеме следящего АЦП также предусмотрен управляющий сигнал Busy. Поскольку сигнал с выхода компаратора в зависимости от направления счета постоянно меняет свое значение с единицы на нуль, то для фиксации момента окончания первого следящего преобразования (момент времени  ) в виде нулевого значения сигнала Busy и удержания его в дальнейшем в структуре АЦП предусмотрен D -триггер DD6 с динамическим управлением и статическими входами установки в нуль и единицу.

) в виде нулевого значения сигнала Busy и удержания его в дальнейшем в структуре АЦП предусмотрен D -триггер DD6 с динамическим управлением и статическими входами установки в нуль и единицу.

) (рисунок 22.6 б). По этому сигналу осуществляется установка в единичное состояние RS -триггера DD4.0 самого старшего разряда

) (рисунок 22.6 б). По этому сигналу осуществляется установка в единичное состояние RS -триггера DD4.0 самого старшего разряда  выходного кода. Триггеры DD4.1... DD4.n-1 остальных разрядов

выходного кода. Триггеры DD4.1... DD4.n-1 остальных разрядов  ... D 0через элементы ИЛИ DD3.1...DD3.n-1 сбрасываются в нулевое состояние.

... D 0через элементы ИЛИ DD3.1...DD3.n-1 сбрасываются в нулевое состояние. то на выходе компаратора DA1 формируется логическая единица, которая проходит через открытый элемент И DD2.0 на вход сброса R триггера DD4.0 и устанавливает его в нулевое состояние. В самом старшем разряде выходного кода формируется логический нуль.

то на выходе компаратора DA1 формируется логическая единица, которая проходит через открытый элемент И DD2.0 на вход сброса R триггера DD4.0 и устанавливает его в нулевое состояние. В самом старшем разряде выходного кода формируется логический нуль. , то на выводе компаратора формируется логический нуль, элемент DD2.0 Скрывается и триггер DD4.0 сохраняет единичное состояние.

, то на выводе компаратора формируется логический нуль, элемент DD2.0 Скрывается и триггер DD4.0 сохраняет единичное состояние. и установленным единичным значением разряда

и установленным единичным значением разряда  . Новое сформированное напряжение с выхода ЦАП поступает на компаратор. При этом если выполняется условие

. Новое сформированное напряжение с выхода ЦАП поступает на компаратор. При этом если выполняется условие  , то на выходе компаратора вновь формируется логическая единица, которая проходит через открытый элемент DD2.1 и элемент DD3.1, и сбрасывает триггер DD4.1 в нулевое состояние.

, то на выходе компаратора вновь формируется логическая единица, которая проходит через открытый элемент DD2.1 и элемент DD3.1, и сбрасывает триггер DD4.1 в нулевое состояние. , компаратор формирует напряжение логического нуля и триггер сохраняет установленное единичное состояние. Таким образом, триггер DD4.1 фиксирует значение разряда

, компаратор формирует напряжение логического нуля и триггер сохраняет установленное единичное состояние. Таким образом, триггер DD4.1 фиксирует значение разряда  .Процесс будет продолжаться в сторону убывания разрядов

.Процесс будет продолжаться в сторону убывания разрядов  , до тех пор, пока не сформируются значения всех разрядов выходного двоичного кода (момент времени

, до тех пор, пока не сформируются значения всех разрядов выходного двоичного кода (момент времени  ).

). определяется только частотой следования импульсов тактового генератора и количеством разрядов выходного кода. При этом от формы входного аналогового сигнала это время не зависит, т.е. оно постоянно. Поэтому для определения момента завершения преобразования можно просто воспользоваться техническими характеристиками АЦП. Тем не менее для облегчения синхронизации работы АЦП с другими устройствами предусмотрен выходной управляющий сигнал Busy, формируемый триггером DD6.

определяется только частотой следования импульсов тактового генератора и количеством разрядов выходного кода. При этом от формы входного аналогового сигнала это время не зависит, т.е. оно постоянно. Поэтому для определения момента завершения преобразования можно просто воспользоваться техническими характеристиками АЦП. Тем не менее для облегчения синхронизации работы АЦП с другими устройствами предусмотрен выходной управляющий сигнал Busy, формируемый триггером DD6. в определенных пределах и значения интеграла опорного напряжения

в определенных пределах и значения интеграла опорного напряжения  в тех пределах, при которых разница этих двух интегралов дает нулевой результат. В качестве результата аналого-цифрового преобразования принимается двоичный код X, пропорциональный пределам интегрирования опорного напряжения. Математически это можно записать

в тех пределах, при которых разница этих двух интегралов дает нулевой результат. В качестве результата аналого-цифрового преобразования принимается двоичный код X, пропорциональный пределам интегрирования опорного напряжения. Математически это можно записать ;

; .

. тактовыми импульсами и подсчета их двоичным счетчиком. Для определенности пределов интегрирования такими же импульсами заполняется и интервал времени

тактовыми импульсами и подсчета их двоичным счетчиком. Для определенности пределов интегрирования такими же импульсами заполняется и интервал времени  . Этот интервал должен быть одинаковым при любом преобразовании и обычно выбирается соответствующим модулю счета

. Этот интервал должен быть одинаковым при любом преобразовании и обычно выбирается соответствующим модулю счета  используемого двоичного счетчика.

используемого двоичного счетчика.

, на выходе компаратора формируется нулевой логический уровень, который закрывает стробирующий элемент И DD1, в результате чего импульсы с выхода генератора GN на счетчик DD2 не проходят. Преобразование начинается с подачи на вход Start схемы единичного импульса (момент времени

, на выходе компаратора формируется нулевой логический уровень, который закрывает стробирующий элемент И DD1, в результате чего импульсы с выхода генератора GN на счетчик DD2 не проходят. Преобразование начинается с подачи на вход Start схемы единичного импульса (момент времени  ) (рисунок 22.7 б).

) (рисунок 22.7 б). .

. и сформированный цифровой код X прямо пропорционален входному аналоговому напряжению. АЦП двухтактного интегрирования, так же как и АЦП последовательного счета, обладает не высоким быстродействием, поскольку выходной код формируется процессом подсчета тактовых импульсов, длительность которого зависит от амплитуды входного аналогового сигнала. Для облегчения синхронизации работы такого АЦП с другими устройствами схема управления обычно формирует сигнал Busy, назначение которого уже было рассмотрено в прежних схемах. Между тем двухтактный интегрирующий АЦП обладает существенным достоинством. По причине интегрирования входного сигнала осуществляется фильтрация высокочастотных помех. Кроме того, период интегрирования

и сформированный цифровой код X прямо пропорционален входному аналоговому напряжению. АЦП двухтактного интегрирования, так же как и АЦП последовательного счета, обладает не высоким быстродействием, поскольку выходной код формируется процессом подсчета тактовых импульсов, длительность которого зависит от амплитуды входного аналогового сигнала. Для облегчения синхронизации работы такого АЦП с другими устройствами схема управления обычно формирует сигнал Busy, назначение которого уже было рассмотрено в прежних схемах. Между тем двухтактный интегрирующий АЦП обладает существенным достоинством. По причине интегрирования входного сигнала осуществляется фильтрация высокочастотных помех. Кроме того, период интегрирования  входного напряжения можно выбрать таким, чтобы почти полностью исключить помехи с частотами, кратными

входного напряжения можно выбрать таким, чтобы почти полностью исключить помехи с частотами, кратными  . Для этой цели обычно выбирается временной интервал, определяемый частотой бытовой сети. Отсюда следует, что АЦП с двойным интегрированием целесообразно применять для оцифровки аналоговых сигналов, характеризующихся сверхнизкими частотами.

. Для этой цели обычно выбирается временной интервал, определяемый частотой бытовой сети. Отсюда следует, что АЦП с двойным интегрированием целесообразно применять для оцифровки аналоговых сигналов, характеризующихся сверхнизкими частотами. компараторов, где п – число разрядов выходного двоичного кода (рисунок 22.8). Пороговые уровни задаются резистивным делителем, состоящим из

компараторов, где п – число разрядов выходного двоичного кода (рисунок 22.8). Пороговые уровни задаются резистивным делителем, состоящим из  одинаковых резисторов R, делящим опорное напряжение

одинаковых резисторов R, делящим опорное напряжение  на т равных значений. Если на входе j- го компаратора амплитуда входного аналогового сигнала

на т равных значений. Если на входе j- го компаратора амплитуда входного аналогового сигнала  превышает текущий квантованный уровень, то на его выходе формируется логическая единица. В противном случае на выходе этого компаратора формируется логический нуль. Сигналы с выходов всех компараторов поступают на вход быстродействующего двоичного шифратора DD1. На выходе этого шифратора формируется двоичный код, соответствующий максимальному номеру входа, на который поступает логическая единица с выхода соответствующего компаратора.

превышает текущий квантованный уровень, то на его выходе формируется логическая единица. В противном случае на выходе этого компаратора формируется логический нуль. Сигналы с выходов всех компараторов поступают на вход быстродействующего двоичного шифратора DD1. На выходе этого шифратора формируется двоичный код, соответствующий максимальному номеру входа, на который поступает логическая единица с выхода соответствующего компаратора.

таких АЦП может достигать сотен МГц, что делает их незаменимыми в радиотехнике. Между тем очевиден недостаток параллельных АЦП: слишком сложная аппаратная реализация, связанная с большим количеством компараторов и резисторов делителя, геометрически возрастающим с увеличением разрядности выходного кода. Поэтому параллельные АЦП имеют обычно не высокую разрядность выходного кода.

таких АЦП может достигать сотен МГц, что делает их незаменимыми в радиотехнике. Между тем очевиден недостаток параллельных АЦП: слишком сложная аппаратная реализация, связанная с большим количеством компараторов и резисторов делителя, геометрически возрастающим с увеличением разрядности выходного кода. Поэтому параллельные АЦП имеют обычно не высокую разрядность выходного кода. .

.