Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Статическое оперативное запоминающее устройство. Динамическое оперативное запоминающее устройство. Постоянное запоминающее устройство.

Основой ячейки памяти в ЗУ статического типа является триггер. В качестве базовых элементов для реализации триггера используются полевые транзисторы. Использование полевых транзисторов обусловлено тем, что они потребляют меньшую мощность, чем биполярные транзисторы, следовательно, и построенные на их основе микросхемы памяти являются более экономичными. На рисунке 19.1 представлен триггер на МОП-транзисторах с индуцируемым p -каналом. Для отпирания такого транзистора напряжение на его затворе относительно истока должно быть меньше нуля: Пусть в исходном состоянии транзистор VT3 открыт, a VT1 закрыт (состояние хранения нуля). Транзисторы VT2 и VT4 выполняют роль резисторов, поэтому на стоке транзистора VT3 будет потенциал напряжения питания

Рисунке 19.1 – Принципиальная схема ячейки ОЗУ статического типа Для установления триггера в единичное состояние (запись единицы) на линию Для записи нуля необходимо при нулевом напряжении на линии А подать напряжение

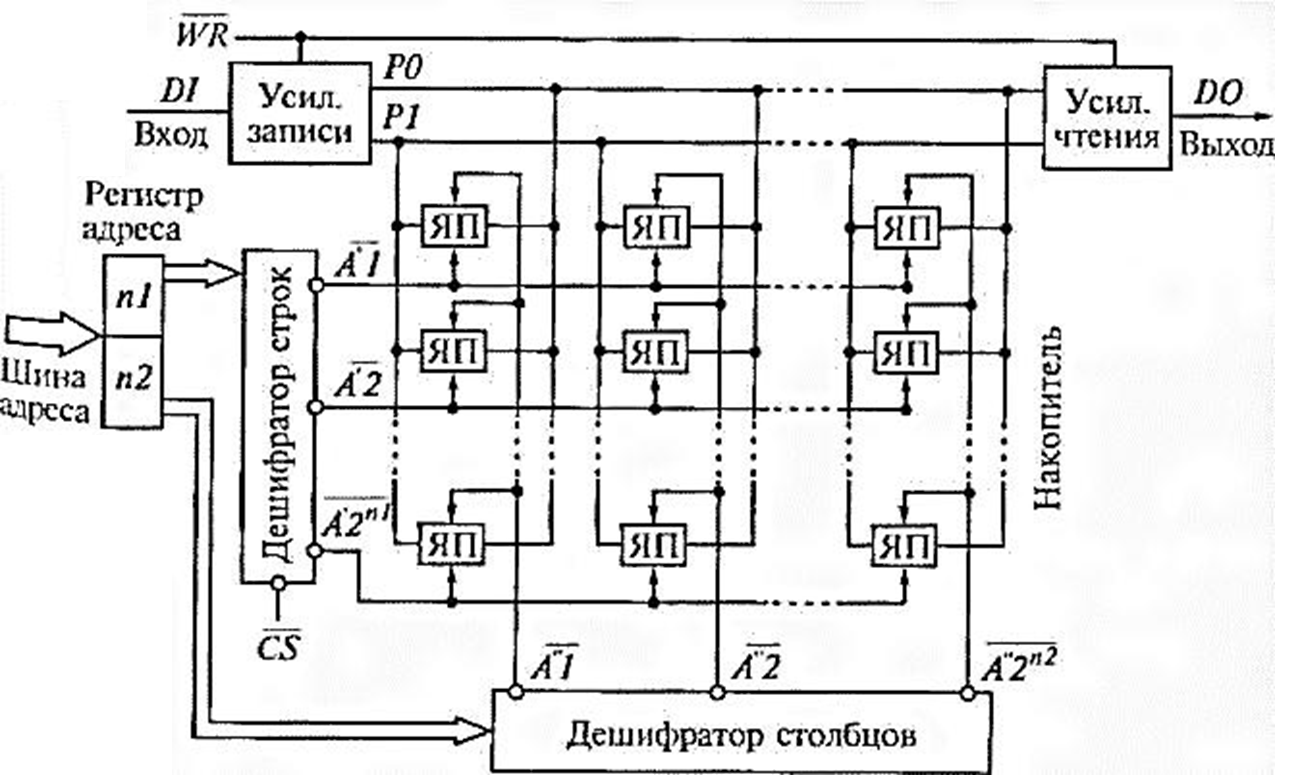

Для считывания информации, предварительно записанной в триггер, необходимо подать нулевой потенциал только на линию. При этом если был открыт транзистор VT1 (единичное состояние), то отрицательным напряжением На рисунке 19.2 приведена типичная структура микросхемы ОЗУ статического типа. Информация хранится в накопителе. Накопитель представляет собой матрицу, составленную из ячеек памяти рассмотренных выше. Для поиска требуемой ячейки памяти указываются строка и столбец, соответствующие положению ячейки памяти в накопителе.

Рисунок 19.2 – Структура микросхемы ОЗУ статистического типа Адрес ячейки памяти (ЯП) в виде двоичного числа принимается по шине адреса в регистр адреса. Число разрядов адреса связано с емкостью накопителя. Число строк и столбцов накопителя выбираются равными целой степени двух. Если число строк Разряды регистра адреса подразделяются на две группы. Одна группа в n1 разрядов определяет двоичный номер строки, в которой расположена ячейка памяти, другая группа в n2 разрядов определяет двоичный номер столбца, в котором находится ячейка памяти. Каждая группа разрядов адреса подается на соответствующий дешифратор строк или столбцов. При этом каждый из дешифраторов создает на одной из своих выходных цепей уровень логического нуля. На остальных выходах устанавливается уровень логической единицы. Ячейка памяти, оказавшаяся под воздействием двух логических нулей на соответствующих линиях

В режиме считывания содержимое ячейки памяти выдается на усилитель считывания и с него на выход микросхемы DO. При этом сигнал записи Указанные процессы происходят, если на входе Первым как в режиме записи, так и в режиме считывания на шину адреса должен выставляться адрес активизируемой ячейки памяти. Снимается адрес с шины после того, как запись в ячейку или чтение из ячейки завершено.

Рисунок 19.3 – Временные диаграммы работы ОЗУ статического типа Один из управляющих сигналов На рисунке 19.3 приведены временные диаграммы работы ОЗУ в случае смены режима, т.е. режим считывания осуществляется после режима записи, а режим записи – после режима считывания. Поэтому происходит установка обоих сигналов Обычно при нескольких режимах чтения подряд и при отсутствии обращения к микросхеме памяти сигнал Считывание информации из микросхемы памяти возможно только в интервал времени В режиме записи сигнал

Микросхемы ОЗУ допускают наращивание емкости памяти как путем наращивания числа хранимых слов, так и путем наращивания разрядности этих слов. На практике часто используется комбинированная структура, объединяющая наращивание, как разрядности, так и количества хранимых слов. В этом случае формируется некоторое количество однотипных групп микросхем, объединенных в структуру с наращиванием разрядности слов. Далее эти группы объединяются в единую структуру с наращиванием количества хранимых слов. Динамическое оперативное запоминающее устройство. Как уже отмечалось, информация в ячейке динамического ОЗУ представлена в виде наличия или отсутствия заряда на конденсаторе. Схема ячейки памяти динамического ЗУ на одном МОП – транзисторе с индуцируемым

Рисунке 19.4 – Принципиальная схема ячейки ОЗУ динамического типа с элементами записи и усилителя считывания На схеме также показаны общие элементы для Поскольку шина данных ШД объединяет все ячейки памяти данного столбца, то она характеризуется большой длиной и ее собственная емкость имеет существенное значение. Поэтому при открывании транзистора

На рисунке 19.5 показан пример структуры микросхемы динамического ОЗУ емкостью 64 Кбит. Данные в этой микросхеме памяти представлены как 64 К отдельных бит, т.е. формат памяти 64

Рисунок 19.5 – Структура микросхемы ОЗУ динамического типа Мультиплексирование позволяет сократить количество выводов микросхемы. Ячейки памяти расположены в виде матрицы из 128 строк и 512 столбцов. На рисунке 19.6 представлены временные диаграммы, поясняющие работу динамического ОЗУ. В режиме считывания на адресные входы микросхемы подаются восемь младших разрядов

Рисунок 19.6 – Временные диаграммы работы ОЗУ динамического типа

В режиме записи за время цикла записи Для каждого типа микросхем динамических ОЗУ в справочниках приводятся временные параметры, регламентирующие длительность управляющих сигналов, подаваемых на микросхему, а также порядок их взаимного следования. Заряд конденсатора динамического ОЗУ со временем уменьшается вследствие утечки, поэтому для сохранения содержимого памяти процесс регенерации каждой ячейки памяти должен производится через определенное время. Следовательно, для предотвращения разряда запоминающих конденсаторов необходимо обращаться к каждой строке матрицы через определенное время. При обычном режиме работы ОЗУ это условие не соблюдается, так как обращение к одним ячейкам происходит часто, а к другим очень редко. Поэтому необходим специальный блок, ответственный за регенерацию памяти. Для правильной работы динамического ОЗУ требуется довольно сложная схема управления. Вследствие того, что обращение к ОЗУ со стороны устройств, с которыми оно работает, и обращение со стороны схемы регенерации не зависит один от другого, следовательно, могут возникать одновременно, то необходимая схема, обеспечивающая упорядоченность этих обращений. Для этих целей существует схемы, управляющие работой динамических ОЗУ, реализованные на одном кристалле. Их использование позволяет значительно упростить построение памяти на динамических ОЗУ. Постоянное запоминающее устройство предназначено для долговременного хранения информации, не разрушаемой при отключении питания. Принцип работы ПЗУ поясняет схема, изображенная на рисунке 19.7. Таким образом, информация, хранимая в ПЗУ, определяется расположением диодов в пересечениях горизонтальных и вертикальных линий. При этом необходимое расположение диодов можно организовать двумя путями. В первом случае запись необходимой информации выполняется в ходе технологического процесса изготовления ПЗУ с использованием маскирующих фотошаблонов, причем запись информации производится в соответствии с технической документацией на данное ПЗУ. Такие ПЗУ называются масочными. Примерами таких ПЗУ являются ПЗУ с записанными программами работы станков с числовым управлением, преобразователи кодов и ряд других случаев, когда одна и та же информация используется в процессе работы множества однотипных устройств.

Рисунок 19.7 – Структура схема масочного ПЗУ Во втором случае запись в ПЗУ осуществляет сам пользователь. Такие ПЗУ называются прожигаемыми ПЗУ. Запись информации в них производится с помощью специальных устройств, называемых программаторами. В процессе изготовления прожигаемых ПЗУ диоды устанавливаются во всех без исключения точках пересечения вертикальных и горизонтальных линий. Последовательно с каждым диодом включены плавкие перемычки, изготавливаемые из материала с относительно большим удельным сопротивлением, обычно из поликристаллического кремния или нихрома. Если через горизонтальную и вертикальную линии пропустить импульс тока порядка 20 мА и длительностью 1 мс, то плавкая перемычка выгорает и соответствующий диод оказывается отключенным. Очевидно, что однажды записанная таким образом информация не может быть изменена. В реальных микросхемах ПЗУ вместо диодов обычно используются биполярные или полевые транзисторы. Отдельным классом ПЗУ выделяют перепрограммируемые ПЗУ (ППЗУ), которые допускают стирание записанной информации и запись новой. Схема ППЗУ почти полностью совпадает с ранее рассмотренной схемой ПЗУ с той разницей, что в точках пересечения горизонтальных и вертикальных линий вместо диодов включены специальные МДП – транзисторы с так называемым изолированным затвором. В обычном состоянии участок исток-сток транзистора электрический ток не проводит. Однако если приложить между истоком и стоком большое напряжение (приблизительно 80 В), то затвор зарядится в результате инжекции электронов. Такой процесс называется зарядкой через влияние. В дальнейшем заряд затвора будет сохраняться достаточно долго. Благодаря весьма высокому качеству диэлектрика из двуокиси кремния при температуре Стирание информации производится путем подачи специальных электрических сигналов в течение определенного времени. В качестве соединительного транзистора в электрически стираемых ППЗУ используется МНОП-транзистор. Он имеет следующую структуру: металл – нитрид кремния – оксид – полупроводник. Между затвором и полупроводником находятся два разных слоя диэлектрика. Использование таких ППЗУ позволяет осуществлять процесс программирования, не извлекая микросхему из устройства, в котором она эксплуатируется. Контрольные вопросы 1 Провидите сравнительный анализ БИС ОЗУ статического и динамического типов. 2 Поясните принцип функционирования ячейки ОЗУ статического типа. 3 Какие функции в микросхеме памяти выполняют дешифраторы строк и столбцов? 4 Какая общая последовательность подачи управляющих сигналов на микросхемы ОЗУ статического типа в режиме считывания и записи? 5 Какие способы увеличения объема хранимой информации при организации модулей оперативной памяти вам известны? 6 Поясните принципы функционирования микросхем ОЗУ динамического типа. 7 Как организуется хранение информации в микросхемах ПЗУ? 8 Как реализуется возможность записи информации в прожигаемые ПЗУ? 9 Каким образом реализуются стирание и запись информации в ППЗУ?

Лекция 20

|

|||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 832; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 52.14.126.74 (0.052 с.) |

.

. , а на стоке транзистора VT1 – нулевой потенциал. Транзисторы VT5 и VT6 осуществляют запись и считывание информации. В режиме хранения данных напряжения на разрядных линиях P0 и P1 равны нулю, а на линии

, а на стоке транзистора VT1 – нулевой потенциал. Транзисторы VT5 и VT6 осуществляют запись и считывание информации. В режиме хранения данных напряжения на разрядных линиях P0 и P1 равны нулю, а на линии  потенциал равен напряжению питания схемы

потенциал равен напряжению питания схемы  . При этом напряжение сток-исток

. При этом напряжение сток-исток  на транзисторе VT5 равно нулю,

на транзисторе VT5 равно нулю,  и транзистор VT5 закрыт. Напряжение

и транзистор VT5 закрыт. Напряжение  транзистора VT6 равно нулю и он также закрыт.

транзистора VT6 равно нулю и он также закрыт.

подается нулевой потенциал, а на разрядную линию P1 потенциал равный

подается нулевой потенциал, а на разрядную линию P1 потенциал равный  . При этом транзистор VT5 будет включен инверсно, т. е. истоком становится вывод, подсоединенный к разрядной линии P1. Напряжение затвор-исток инверсно включенного транзистора VT5 становится меньше нуля

. При этом транзистор VT5 будет включен инверсно, т. е. истоком становится вывод, подсоединенный к разрядной линии P1. Напряжение затвор-исток инверсно включенного транзистора VT5 становится меньше нуля  и транзистор VT5 открывается. Положительный сигнал поступает на затвор транзистора VT3, при этом

и транзистор VT5 открывается. Положительный сигнал поступает на затвор транзистора VT3, при этом  становится равным нулю и транзистор VT3 закрывается. В результате на затвор транзистора VT1 поступает нулевой потенциал. У этого транзистора

становится равным нулю и транзистор VT3 закрывается. В результате на затвор транзистора VT1 поступает нулевой потенциал. У этого транзистора  становится отрицательным, и транзистор VT1 открывается, на его стоке устанавливается положительное напряжение, что соответствует единичному состоянию триггера. Напряжение на стоке VT3 становится равным нулю.

становится отрицательным, и транзистор VT1 открывается, на его стоке устанавливается положительное напряжение, что соответствует единичному состоянию триггера. Напряжение на стоке VT3 становится равным нулю. на разрядную линию P0, при этом через открытый транзистор VT6 положительное напряжение, попадая на затвор транзистора VT1, запирает его, что приводит к открыванию транзистора VT3. На стоке транзистора VT1 установится нулевой потенциал, а на стоке транзистора VT3 – потенциал напряжения питания.

на разрядную линию P0, при этом через открытый транзистор VT6 положительное напряжение, попадая на затвор транзистора VT1, запирает его, что приводит к открыванию транзистора VT3. На стоке транзистора VT1 установится нулевой потенциал, а на стоке транзистора VT3 – потенциал напряжения питания. будет открыт транзистор VT5 и через него высокий потенциал поступит в разрядную линию P1. Если триггер находится в состоянии нуля, то откроется транзистор VT6 и высокий потенциал поступит в разрядную линию Р0.

будет открыт транзистор VT5 и через него высокий потенциал поступит в разрядную линию P1. Если триггер находится в состоянии нуля, то откроется транзистор VT6 и высокий потенциал поступит в разрядную линию Р0.

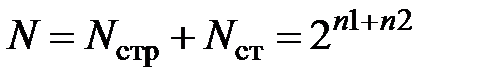

и число столбцов

и число столбцов  , то общее число ячеек памяти (емкость накопителя)

, то общее число ячеек памяти (емкость накопителя)  , где

, где  – число разрядов адреса, принимаемого в регистр адреса. Например, при емкости

– число разрядов адреса, принимаемого в регистр адреса. Например, при емкости  число разрядов адреса

число разрядов адреса  . При этом выбирается

. При этом выбирается  . В этом случае число строк и число столбцов накопителя равно

. В этом случае число строк и число столбцов накопителя равно  . Требуемая размерность матрицы накопителя –

. Требуемая размерность матрицы накопителя –  .

. и

и  одновременно, является выбранной. Этому соответствует подача логического нуля на линию

одновременно, является выбранной. Этому соответствует подача логического нуля на линию  триггера ячейки памяти, рассмотренной выше.

триггера ячейки памяти, рассмотренной выше. должен иметь пассивный единичный уровень. Режим записи устанавливается подачей активного нулевого уровня сигнала на вход записи

должен иметь пассивный единичный уровень. Режим записи устанавливается подачей активного нулевого уровня сигнала на вход записи  . Открывается усилитель записи, и бит информации с входа данных DI поступает в выбранную ячейку памяти для запоминания, при этом усилитель считывания закрывается и данные на выход DO схемы не поступают.

. Открывается усилитель записи, и бит информации с входа данных DI поступает в выбранную ячейку памяти для запоминания, при этом усилитель считывания закрывается и данные на выход DO схемы не поступают. выбора микросхемы действует активный уровень логического нуля. При уровне логической единицы на этом входе на всех выходах дешифратора строк устанавливается уровень логической единицы, и ЗУ оказывается в режиме хранения. Последовательность подачи управляющих сигналов индивидуальна для каждого типа микросхемы памяти. Между тем имеются общие закономерности. Рассмотрим последовательность подачи сигналов управления в режимах чтения и записи (рисунок 19.3).

выбора микросхемы действует активный уровень логического нуля. При уровне логической единицы на этом входе на всех выходах дешифратора строк устанавливается уровень логической единицы, и ЗУ оказывается в режиме хранения. Последовательность подачи управляющих сигналов индивидуальна для каждого типа микросхемы памяти. Между тем имеются общие закономерности. Рассмотрим последовательность подачи сигналов управления в режимах чтения и записи (рисунок 19.3).

записи, или

записи, или  выбора микросхемы, или оба должны устанавливаться в активное состояние после установки адреса (интервалы времени,

выбора микросхемы, или оба должны устанавливаться в активное состояние после установки адреса (интервалы времени,

и

и  ,

,  ) и сниматься до снятия адреса (интервалы времени

) и сниматься до снятия адреса (интервалы времени  ,

,  и

и  ,

,  ). Тем самым обеспечивается высокоимпедансное состояние выводов DO и DI микросхемы, что исключает возможность ложного обмена информацией между микросхемами памяти и устройствами при смене адресов. В случае пассивного уровня сигнала

). Тем самым обеспечивается высокоимпедансное состояние выводов DO и DI микросхемы, что исключает возможность ложного обмена информацией между микросхемами памяти и устройствами при смене адресов. В случае пассивного уровня сигнала  отключается соответствующий буферный усилитель считывания или записи в каждом из своих режимах. В случае же пассивного уровня сигнала

отключается соответствующий буферный усилитель считывания или записи в каждом из своих режимах. В случае же пассивного уровня сигнала  вырабатывается единичный уровень сигнала на линии

вырабатывается единичный уровень сигнала на линии  ячейки памяти, благодаря чему она отключается от линий P0) и P1 хранит записанную информацию.

ячейки памяти, благодаря чему она отключается от линий P0) и P1 хранит записанную информацию. и

и  .

. имеет постоянное значение логической единицы. В этом случае активизация входа DO осуществляется только нулевым уровнем сигнала на входе

имеет постоянное значение логической единицы. В этом случае активизация входа DO осуществляется только нулевым уровнем сигнала на входе  . Первым определяется режим работы памяти, т.е. подается сигнал

. Первым определяется режим работы памяти, т.е. подается сигнал  . Управление выводами DI и DO осуществляется сигналом

. Управление выводами DI и DO осуществляется сигналом  , который подается внутри временного интервала действия сигнала

, который подается внутри временного интервала действия сигнала  .

. , когда завершился процесс формирования данных на выходе DO (интервал времени

, когда завершился процесс формирования данных на выходе DO (интервал времени  ), и пока не снят сигнал

), и пока не снят сигнал  выбора микросхемы. При этом время выборки

выбора микросхемы. При этом время выборки  характеризуется временным интервалом с момента выставления сигнала

характеризуется временным интервалом с момента выставления сигнала  и до момента формирования информации на выходе DO.

и до момента формирования информации на выходе DO. должен выставляться только тогда, когда записываемые данные готовы и поступили на вход DI (временной интервал

должен выставляться только тогда, когда записываемые данные готовы и поступили на вход DI (временной интервал  ). Аналогично сами данные для записи должны быть подготовлены к моменту, когда выработается активный уровень сигнала

). Аналогично сами данные для записи должны быть подготовлены к моменту, когда выработается активный уровень сигнала  (временной интервал

(временной интервал  ), и удержаны до окончания действия этого сигнала.

), и удержаны до окончания действия этого сигнала. -каналом представлена на рисунок 19.4 (выделена пунктирной линией).

-каналом представлена на рисунок 19.4 (выделена пунктирной линией).

– ячеек одного столбца. Главное достоинство этой схемы – малая занимаемая площадь. Накопительный конденсатор

– ячеек одного столбца. Главное достоинство этой схемы – малая занимаемая площадь. Накопительный конденсатор  имеет МДП-структуру и изготовляется в едином технологическом цикле. Величина его емкости составляет сотые доли пФ. Конденсатор

имеет МДП-структуру и изготовляется в едином технологическом цикле. Величина его емкости составляет сотые доли пФ. Конденсатор  хранит информационный заряд. Транзистор

хранит информационный заряд. Транзистор  выполняет роль переключателя, передающего заряд конденсатора в разрядную шину данных ШД при считывании либо заряжающего конденсатор при записи. В режиме хранения на адресной линии

выполняет роль переключателя, передающего заряд конденсатора в разрядную шину данных ШД при считывании либо заряжающего конденсатор при записи. В режиме хранения на адресной линии  должен присутствовать потенциал логической единицы, под действием которого транзистор

должен присутствовать потенциал логической единицы, под действием которого транзистор  будет закрыт

будет закрыт  и конденсатор

и конденсатор  отключен от шины данных ШД. Включение конденсатора в шину данных осуществляется логическим нулем на линии

отключен от шины данных ШД. Включение конденсатора в шину данных осуществляется логическим нулем на линии  . При этом на транзистор

. При этом на транзистор  что приводит к его открыванию.

что приводит к его открыванию. потенциал шины данных изменяется незначительно. Чтобы установившийся потенциал на ШД однозначно идентифицировать с уровнем напряжения логического нуля или логической единицы, используется усилитель на базе транзистора

потенциал шины данных изменяется незначительно. Чтобы установившийся потенциал на ШД однозначно идентифицировать с уровнем напряжения логического нуля или логической единицы, используется усилитель на базе транзистора  и резистора

и резистора  . Непосредственно перед считыванием емкость шины данных подзаряжают подключением ее к источнику питания через транзистор

. Непосредственно перед считыванием емкость шины данных подзаряжают подключением ее к источнику питания через транзистор  . Делается это для фиксации потенциала шины данных. При считывании информации происходит перераспределение заряда конденсатора и заряда шины данных, в результате чего информация, хранимая на конденсаторе

. Делается это для фиксации потенциала шины данных. При считывании информации происходит перераспределение заряда конденсатора и заряда шины данных, в результате чего информация, хранимая на конденсаторе  , разрушается. Поэтому в цикле считывания необходимо произвести восстановление (регенерацию) заряда конденсатора. Для этих целей, а также для записи в ячейку памяти новых значений, используются транзисторы

, разрушается. Поэтому в цикле считывания необходимо произвести восстановление (регенерацию) заряда конденсатора. Для этих целей, а также для записи в ячейку памяти новых значений, используются транзисторы  и

и  , которые подключают шину данных либо к источнику питания, либо к нулевому общему потенциалу. Для записи в ячейку памяти логической единицы необходимо открыть транзистор

, которые подключают шину данных либо к источнику питания, либо к нулевому общему потенциалу. Для записи в ячейку памяти логической единицы необходимо открыть транзистор  нулевым значением управляющего сигнала

нулевым значением управляющего сигнала  и подключить к шине данных источник питания. Для записи логического нуля необходимо нулевым потенциалом на входе

и подключить к шине данных источник питания. Для записи логического нуля необходимо нулевым потенциалом на входе  открыть транзистор

открыть транзистор  . Одновременная подача логических нулей на входы

. Одновременная подача логических нулей на входы  и

и  не допускается, так как это вызовет короткое замыкание источника питания на общий провод заземления.

не допускается, так как это вызовет короткое замыкание источника питания на общий провод заземления. . Ввод и вывод осуществляется раздельно, для чего предусмотрена пара выводов

. Ввод и вывод осуществляется раздельно, для чего предусмотрена пара выводов  и

и  . Для ввода адреса имеется восемь контактов

. Для ввода адреса имеется восемь контактов  . Адресация к 64 К ячейкам памяти осуществляется шестнадцатиразрядными адресами

. Адресация к 64 К ячейкам памяти осуществляется шестнадцатиразрядными адресами  . Причем сначала на входы

. Причем сначала на входы  подаются восемь младших разрядов

подаются восемь младших разрядов  адреса, а затем – восемь старших разрядов

адреса, а затем – восемь старших разрядов  . Восемь младших разрядов адреса фиксируются в регистре адреса строки подачей сигнала

. Восемь младших разрядов адреса фиксируются в регистре адреса строки подачей сигнала  (сигнал выборки строки). Восемь старших разрядов адреса фиксируются в регистре адреса столбца подачей сигнала

(сигнал выборки строки). Восемь старших разрядов адреса фиксируются в регистре адреса столбца подачей сигнала  (сигнал выборки столбца). Такой режим передачи кода адреса называется мультиплексированным по времени.

(сигнал выборки столбца). Такой режим передачи кода адреса называется мультиплексированным по времени.

адреса, после чего вырабатывается сигнал

адреса, после чего вырабатывается сигнал  , при этом производится выбор строки матрицы в соответствии с поступившим адресом. У всех ячеек памяти выбранной строки регенерируется заряд конденсаторов. Далее производится подача на адресные входы микросхемы восьми старших разрядов

, при этом производится выбор строки матрицы в соответствии с поступившим адресом. У всех ячеек памяти выбранной строки регенерируется заряд конденсаторов. Далее производится подача на адресные входы микросхемы восьми старших разрядов  адреса, после чего вырабатывается сигнал

адреса, после чего вырабатывается сигнал  . Этим сигналом выбирается нужная ячейка памяти из выбранной строки и считанный бит информации поступает на выход микросхемы

. Этим сигналом выбирается нужная ячейка памяти из выбранной строки и считанный бит информации поступает на выход микросхемы  . В режиме считывания промежуток времени между подачей сигнала

. В режиме считывания промежуток времени между подачей сигнала  и появлением данных на выходе

и появлением данных на выходе  называется временем выборки

называется временем выборки  .

.

принимается интервал времени между появлением сигнала

принимается интервал времени между появлением сигнала  и окончанием сигнала

и окончанием сигнала  . В момент появления сигнала

. В момент появления сигнала  записываемые данные уже должны поступать на вход

записываемые данные уже должны поступать на вход  . Сигнал

. Сигнал  обычно вырабатывается раньше сигнала

обычно вырабатывается раньше сигнала  .

.

заряд уменьшается на 70% первоначального значения примерно за 10 лет. Отрицательный заряд на затворе притягивает дырки, создает в «

заряд уменьшается на 70% первоначального значения примерно за 10 лет. Отрицательный заряд на затворе притягивает дырки, создает в « -области проводящий

-области проводящий  -канал между истоком и стоком, т.е. транзистор оказывается в проводящем состоянии.

-канал между истоком и стоком, т.е. транзистор оказывается в проводящем состоянии.