Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Схема или - не на мдп и кмдп. ⇐ ПредыдущаяСтр 8 из 8

Схема И - НЕ на МДП и КМДП.

Мультиплексор

Демультиплексор.

4в1,8в1,16в1.

Дешифратор.

Шифратор.

Триггеры, классификация. триггер имеет два устойчивых состояния равновесия - «1» и «0»это запоминающий элемент для временного хранения информации. Имеет два выхода: прямой и инверсный.Классификация:1) RS-триггер с раздельной установкой 0 и 1;2) D-триггер с приемом информации по 1 входу. повторяет входной сигнал с задержкой;3) Т-триггер со счетным входом, переброс триггера происходит с каждым очередным сигналом; 4) DV-, TV- имеют дополнительный вход;5)JK-триггтер - универсальный триггер с раздельной установкой «0» и «1». Наборы 11 не запрещены. 6) комбинированный триггер совмещает несколько режимов; 7)триггер со сложной логикой

D-триггер.

Т-триггер

64.JK-триггер имеет 3 входа:JKC.Но одноступенчатый триггер работает не надежно, т.к. запоминающая ячейка – служит одвременно источником информ(с него поступает сигнал старого состояния) и приемником(переключ в новое сост и стирает старое). Одновременное выполнение 2 операций невозможно.Поэтому исп 2-ступенчатые триггеры. Регистр хранения.

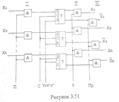

С приходом каждого тактового импульса происходит перезапись содержимого триггеера каждого разряда в соседний без изменения порядка следования «1» и «0».Сдвиговые регистры делятся на:- со сдвигом информации вправо - в сторону младших разрядов;- со сдвигом в сторону старших разрядов; - реверсивные — со сдвигом влево или вправо.Регистры сдвига строятся на RS, JK, D, DV - триггерах, на одно- и двухступенчатых, одно- и многотактные. В 2ступенчатых триггерах 1ая ступень управляется сигналом С, а 2-ая инверсным сигналом (с черт) С. Выходы одних триггеров соединяются со входами других, сдвиг осущ синхроимпульсом. Счетчики суммирующие.

Счетчики вычитающие.

Если рассмотреть таблицу обратного счёта, видно что старший разряд меняет свое состояние при изменении младшего разряда с «0»на«1». В вычитающих счётчиках (3.58) содержание его понижается на 1 с приходом каждого импульса. Счетчик построен на синхронных МS-Т-триггерах. Предварителъно все триттеры устанавливаются в «1» подачей нулевого сигнала на вход S. Десятичный счетчик.

10ичный Счетчик имеет коэффициент пересчета 10. Он считает от 0 до 9. При поступлении на его вход десятого импульса все его выходы устанавливаются в нулевое состояние. В схеме использованы синхронные JK-триггеры. Первый триггер изменяет свое состояние с приходом каждого перепада входного сигнала, так как его J и Kвходы подключены к 1. J-вход второго триггера подключен к инверсному выходу четвертого триггера, а там до прихода восьмого импульса также стоит 1. Этот триггер будет переключаться от 2,4,6,8 импульсов. Третий триггер переключится 4 и 8-ым импульсами. и т.д.

|

|||||||||||

|

Последнее изменение этой страницы: 2017-01-27; просмотров: 481; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.129.39.55 (0.012 с.) |

в двухвходовой схеме ИЛИ-НЕ на МДП (2.32) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подана 1, соответствующий транзистор отпирается, и на выходе схемы будет 0. И только при подаче на все входы схемы 0 транзисторы VT1 и VT2 запрутся, и на выходе появится 1. * Схема ИЛИ-НЕ на КМДП 2.35. Если на оба входа поданы 0, то транзисторы VT 3 и VT 4 будут открыты, так как имеют канал с проводимостью р-типа, а транзисторы VT 1 и VT 2 — закрыты, так как имеют канал с проводимостью n -типа. Установится 1. При подаче 1 хотя бы на один из входов соответствующий транзистор VT 3 или VT 4 закроется, а транзистор VT 1 или VT 2 соответственно откроется. На выходе 0.

в двухвходовой схеме ИЛИ-НЕ на МДП (2.32) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подана 1, соответствующий транзистор отпирается, и на выходе схемы будет 0. И только при подаче на все входы схемы 0 транзисторы VT1 и VT2 запрутся, и на выходе появится 1. * Схема ИЛИ-НЕ на КМДП 2.35. Если на оба входа поданы 0, то транзисторы VT 3 и VT 4 будут открыты, так как имеют канал с проводимостью р-типа, а транзисторы VT 1 и VT 2 — закрыты, так как имеют канал с проводимостью n -типа. Установится 1. При подаче 1 хотя бы на один из входов соответствующий транзистор VT 3 или VT 4 закроется, а транзистор VT 1 или VT 2 соответственно откроется. На выходе 0.

В схеме И-НЕ на МДП (2.33) Если хотя бы на один из входов подан 0, соответствующий транзистор запирается, и на выходе схемы будет 1. И только при подаче на все входы схемы 1 транзисторы VT1 и VT2 откроются, и на выходе будет 0. * В схеме И-НЕ на КМДП (2.33) параллельно соединены транзисторы с каналами р -типа, а последовательно — с каналами п- типа. 0 на выходе устанавливается только при одновременной подаче на оба входа элемента 1, а во всех остальных случаях на выходе будет присутствовать 1. При одновременной подаче на входы x 1 и x 2 1 транзисторы VT 1 и VT 2 открываются, а транзисторы VT 3 и VT 4 закр. На выходе 0. При подаче хотя бы на один из входов 0. На выходе 1.

В схеме И-НЕ на МДП (2.33) Если хотя бы на один из входов подан 0, соответствующий транзистор запирается, и на выходе схемы будет 1. И только при подаче на все входы схемы 1 транзисторы VT1 и VT2 откроются, и на выходе будет 0. * В схеме И-НЕ на КМДП (2.33) параллельно соединены транзисторы с каналами р -типа, а последовательно — с каналами п- типа. 0 на выходе устанавливается только при одновременной подаче на оба входа элемента 1, а во всех остальных случаях на выходе будет присутствовать 1. При одновременной подаче на входы x 1 и x 2 1 транзисторы VT 1 и VT 2 открываются, а транзисторы VT 3 и VT 4 закр. На выходе 0. При подаче хотя бы на один из входов 0. На выходе 1. М-многовходовая КЛС с одним выходом, подключает единственную общую выходную шину к одному из входов в зависимости от управляющего сигнала, заданного двоичным кодом.Применяется для преобразования параллельного кода в последовательный, сравнения кодов и т.д. Бывают 4в1,8в1,16в1.

М-многовходовая КЛС с одним выходом, подключает единственную общую выходную шину к одному из входов в зависимости от управляющего сигнала, заданного двоичным кодом.Применяется для преобразования параллельного кода в последовательный, сравнения кодов и т.д. Бывают 4в1,8в1,16в1. Д- это КЛС, имеющая один информационный вход Ғ, к управляющих входов Vk ..V1 и п информацонных выходов (х1...хn). Коэффициент усиления используется для распределения данных одного канала между несколькими приемниками. Бывают

Д- это КЛС, имеющая один информационный вход Ғ, к управляющих входов Vk ..V1 и п информацонных выходов (х1...хn). Коэффициент усиления используется для распределения данных одного канала между несколькими приемниками. Бывают Д- мног о в ь гх о д н а я к о м б и н а ционная л о ги ч еская схема (КЛС), в кот каждой ком бинации переменных на входе с о о т в е т с тву е т единйчный сигнал только на одном из выходов.Д в ои чные д е ш и ф р а т о р ы преобразуют двоичный код в код «1 из к».В дешифраторе иногда выполняется операция стробирования, разрешающая выработку выходных сигналов с определенным интервалом времени. Дешифратор называется полным, если к = 2п, т.е. реализует все минтермы.

Д- мног о в ь гх о д н а я к о м б и н а ционная л о ги ч еская схема (КЛС), в кот каждой ком бинации переменных на входе с о о т в е т с тву е т единйчный сигнал только на одном из выходов.Д в ои чные д е ш и ф р а т о р ы преобразуют двоичный код в код «1 из к».В дешифраторе иногда выполняется операция стробирования, разрешающая выработку выходных сигналов с определенным интервалом времени. Дешифратор называется полным, если к = 2п, т.е. реализует все минтермы. Шифратор (СД) вьшолняет функцию, обратную функции дешифратора.Двоичный шифратор - КЛС, преобразует код "1 из N" в двоичный. При наличии «1» на одном из входов, появляется n-элементная комбинация на выходе, соответствующая номеру возбужденного входа.Шифратор применяется для ввода данных с клавиатуры, для преобразования в двоичный код номера нажатой кнопки и т.д. Полный двоичный шифратор имеет Nвх =2^ n - входов, где и- число выходов, неполный

Шифратор (СД) вьшолняет функцию, обратную функции дешифратора.Двоичный шифратор - КЛС, преобразует код "1 из N" в двоичный. При наличии «1» на одном из входов, появляется n-элементная комбинация на выходе, соответствующая номеру возбужденного входа.Шифратор применяется для ввода данных с клавиатуры, для преобразования в двоичный код номера нажатой кнопки и т.д. Полный двоичный шифратор имеет Nвх =2^ n - входов, где и- число выходов, неполный

3.42схема тактируемого RS-триггера на логических элементах И-НЕ. На каждом входе запоминающей ячейки есть дополнительная схема совпадения (И-НЕ). Первые входы их объединены, на них подаются синхроимпульсы, на вторые входы -информационные сигналы. При С=0 – состояние тригтера не меняется.

3.42схема тактируемого RS-триггера на логических элементах И-НЕ. На каждом входе запоминающей ячейки есть дополнительная схема совпадения (И-НЕ). Первые входы их объединены, на них подаются синхроимпульсы, на вторые входы -информационные сигналы. При С=0 – состояние тригтера не меняется. Асинхронный D-тригтер имеет 1 вход и 2 выхода, осуществляет задержку сигнала. информация на выходе равна информации на входе на предыдущем такте.В тактируемых триг момент принятия информации определяется тактовым сигналом С. Для правильной работы D-триггера должен быть интервал времени после прихода информации на вход D перед приходом синхросигнала С. 2 входа: D - информационный, С- тактируемый 3.45. При С=1 записывается в триггер то, что было подано на вход В до подачи синхросигнала С.В DV-триггере при V =1 работает как Д, при V=0- сохраняется информация.

Асинхронный D-тригтер имеет 1 вход и 2 выхода, осуществляет задержку сигнала. информация на выходе равна информации на входе на предыдущем такте.В тактируемых триг момент принятия информации определяется тактовым сигналом С. Для правильной работы D-триггера должен быть интервал времени после прихода информации на вход D перед приходом синхросигнала С. 2 входа: D - информационный, С- тактируемый 3.45. При С=1 записывается в триггер то, что было подано на вход В до подачи синхросигнала С.В DV-триггере при V =1 работает как Д, при V=0- сохраняется информация. Имеет 1 информационный вход Т и переключается, когда на вход триггера поступает сигнал. Из характеристического уравнения Qn+1= с чертой ТQ+Tс чертQ видно, что триггер производит сложение по модулю 2. Частота на выходе в 2 раза меньше, чем на входе. Поэтому можно использовать триггер как делитель на два и для построения счетчиков.

Имеет 1 информационный вход Т и переключается, когда на вход триггера поступает сигнал. Из характеристического уравнения Qn+1= с чертой ТQ+Tс чертQ видно, что триггер производит сложение по модулю 2. Частота на выходе в 2 раза меньше, чем на входе. Поэтому можно использовать триггер как делитель на два и для построения счетчиков. 3.51 схема регистра с параллельным приемом и выдачей информации. На вход регистра хранения подается слово Здесь обозначены шины: П - приема, С - синхронизации, В -выдачи, Пр - преобразования информации, Уст. «0» - установка нуля на входах RS-триггеров. Регистр хранения построен на RS-тригтерах с логическими элементами «И».Входы Rвсех тригтеров объединены и соединены с шиной сброса (Уст. «0») Для установки регистра в «0» необходимо одновременно подать «1» по шине Уст «0» и «С».Приём информации или запись. В следующем такте код параллельно поступает на входы логических элементов «И», одновременно сигнал «1» - по шинам П и С. Выходы «И» соединены со входами «S» триггеров.

3.51 схема регистра с параллельным приемом и выдачей информации. На вход регистра хранения подается слово Здесь обозначены шины: П - приема, С - синхронизации, В -выдачи, Пр - преобразования информации, Уст. «0» - установка нуля на входах RS-триггеров. Регистр хранения построен на RS-тригтерах с логическими элементами «И».Входы Rвсех тригтеров объединены и соединены с шиной сброса (Уст. «0») Для установки регистра в «0» необходимо одновременно подать «1» по шине Уст «0» и «С».Приём информации или запись. В следующем такте код параллельно поступает на входы логических элементов «И», одновременно сигнал «1» - по шинам П и С. Выходы «И» соединены со входами «S» триггеров. 66.Регистр сдвига.

66.Регистр сдвига.

Счетчик-послед схема для подсчета числа входных сигналов и хранения 2ичного кода этого числа. Р а сс м о трим последовательность двоичных чисел - таблицу прямого счёта. Видно, что соседний старший разряд изменяет свое состояние при переходе младшего с 1 на 0. Т.е. счётчик состоит из цепочки триггеров с инверсным динамическим управлением (3.56) или двухступенчатых MS -триггеров. В суммирующих счетчиках вначале подачей «1» на вход R триггеры устанавливаются в нулевое состояние. Этот счётчик может быть делителем частоты. Каждый триггер старшего разряда переключается в 2 раза реже младшего.

Счетчик-послед схема для подсчета числа входных сигналов и хранения 2ичного кода этого числа. Р а сс м о трим последовательность двоичных чисел - таблицу прямого счёта. Видно, что соседний старший разряд изменяет свое состояние при переходе младшего с 1 на 0. Т.е. счётчик состоит из цепочки триггеров с инверсным динамическим управлением (3.56) или двухступенчатых MS -триггеров. В суммирующих счетчиках вначале подачей «1» на вход R триггеры устанавливаются в нулевое состояние. Этот счётчик может быть делителем частоты. Каждый триггер старшего разряда переключается в 2 раза реже младшего.

Счетчик-послед схема для подсчета числа входных сигналов и хранения 2ичного кода этого числа.

Счетчик-послед схема для подсчета числа входных сигналов и хранения 2ичного кода этого числа. Счетчик-послед схема для подсчета числа входных сигналов и хранения 2ичного кода этого числа.

Счетчик-послед схема для подсчета числа входных сигналов и хранения 2ичного кода этого числа.