Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Типы архитектуры микропроцессорной системы и классификация микропроцессоровСтр 1 из 19Следующая ⇒

Типы архитектуры микропроцессорной системы и классификация микропроцессоров Классификация МП

И классическая архитектура фон-Неймана и гарвардская архитектура прошли длинный путь развития. В общем смысле под архитектурой процессора понимается его программная модель, то есть программно-видимые свойства. Под микроархитектурой понимается внутренняя реализация этой программной модели. Для одной и той же архитектуры разными фирмами и в разных поколениях применяются существенно различные микроархитектурные реализации. Сейчас существует множество архитектур процессоров, которые делятся на две глобальные категории - RISC и CISC. RISC - Reduced (Restricted) Instruction Set Computer - процессоры (компьютеры) с сокращенной системой команд. Эти процессоры обычно имеют набор однородных регистров универсального назначения, причем их число может быть большим. Система команд отличается относительной простотой, коды инструкций имеют четкую структуру, как правило, с фиксированной длиной. В результате аппаратная реализация такой архитектуры позволяет с небольшими затратами декодировать и выполнять эти инструкции за минимальное (в пределе 1) число тактов синхронизации. Определенные преимущества дает и унификация регистров. CISC - Complete Instruction Set Computer - процессоры (компьютеры) с полным набором инструкций, к которым относится и семейство х86, на котором реализовано подавляющее большинство ПК. Состав и назначение их регистров существенно неоднородны, широкий набор команд усложняет декодирование инструкций, на что расходуются аппаратные ресурсы. Для выполнения инструкций процессора требуется различное и значительное число тактов.Процессоры х86 имеют сложную систему команд, во многом обусловленную необходимостью совместимости с программным обеспечением для IBM PC, имеющим уже 20-летнюю историю. Кроме того, в процессорах семейства х86, начиная с 486, применяется комбинированная архитектура - CISC-процессор имеет RISC-ядро. В рамках рассмотренных архитектур также различают следующие способы организации вычислительного процесса: один поток команд - один поток данных (Simple Instruction - Simple Data, SISD) - характерно для традиционной фон-неймановской архитектуры (иногда вместо Simple пишут Single); один поток команд - множественный поток данных (Simple Instruction - Multiple Data, SIMD) - технология MMX;

множественный поток команд - один поток данных (Multiple Instruction - Simple Data, MISD); множественный поток команд - множественный поток данных (Multiple Instruction - Multiple Data, MIMD). В настоящее время различные фирмы (Intel, Motorola, Atmel, Microchip) выпускают обширную номенклатуру семейств микропроцессоров для различных областей применения. При этом используют несколько способов классификации микропроцессоров: по разрядности, архитектурным особенностям, семействам и т. д. Микропроцессоры, в частности делятся на четыре класса: · универсальные · сигнальные (DSP); · транспьютеры; · микроконтроллеры. Универсальные МП (Intel х86) используются в ЭВМ различного назначения: ПК, серверах, портативных ПК, больших ЭВМ и т. д. Они обладают высокой производительностью операций с фиксированной и плавающей точкой, обрабатывают данные большой разрядности, позволяют адресовать память большого объема, имеют высокие тактовые частоты, развитую систему команд и предназначены для работы на системную шину. Сигнальные МП (DSP – digital signal processor) предназначены для обработки сигналов в реальном масштабе времени и решают типовые задачи вида: фильтрация, спектр-анализ, компрессия и т. д. Эти МП вытесняют аналоговые устройства аналогичного назначения в таких областях как радио, телевидение, связь, мультимедиа. Они имеют модифицированную гарвардскую архитектуру, меньшую разрядность данных, но у них есть набор специальных команд для цифровой обработки сигналов. Транспьютеры предназначены для построения параллельных вычислительных систем, в которых матрицы из N-однотипных МП работают с общим полем памяти. Межпроцессорные связи в этих структурах поддерживаются или сигнальными или коммутационными процессорами. Для параллельных структур разрабатываются специальные методы программирования, которые обеспечивают параллельную работу процессоров. Микроконтроллеры предназначены для встроенных систем управления и работе в реальном масштабе времени, обладают большой специализацией и разнообразием функций, различаются по параметрам и составу периферии, тактовые частоты низкие (до 20 МГц), разрядность 8 – 16 бит. Микроконтроллеры составляют основу автоматизации нижнего уровня.

Все микропроцессоры выполняются в виде интегральной схемы сверхбольшой степени интеграции (СБИС). Обычно СБИС бывают выполнены по КМОП-технологии, что обеспечивает: малое потребление мощности, достаточно высокое быстродействие, высокую помехоустойчивость и широкий диапазон напряжения питания. Буферные каскады микропроцессоров выполняются по технологии ТТЛШ, что обеспечивает подключение большей нагрузки и более высокое быстродействие при работе на емкостную нагрузку. В виде СБИС также выпускаются программируемые логические матрицы различной архитектуры (ПЛИС). Они вместе с логическими микросхемами и микросхемами средней степени интеграции (СИС) используются для построения периферийных узлов МПС. В настоящее время проходит проверку технология, когда в границах одного кристалла возможно сочетание различных типов структур: CPU и ПЛИС.

Архитектура МПС Архитектура микропроцессорной системы в самом общем виде это комплексное понятие, описывающее функциональные возможности аппаратных средств МПС. Реализация этих возможностей для управления процессом вычислений, организации информационного обмена и представления программ и данных возложена на программные средства МПС. Архитектура МПС имеет многоуровневую иерархическую организацию со многими компонентами на каждом уровне. Два нижних уровня представляют физическую и логическую организацию МПС. Для аппаратных средств (АС) физический уровень представляет принципиальная схема, логический уровень представляет структурная схема; для программных средств (ПС) физический уровень – это уровень кодировки данных и программ, а логический уровень представляет структуру вычислительной среды. Основные элементы, определяющие архитектуру МПС: 1. Структура магистралей МПС и организация взаимодействия модулей. 2. Логическая организация и структура пространств памяти и ввода-вывода. 3. Регистровая структура микропроцессора и способы адресации. 4. Система команд микропроцессора. 5. Организация системы прерываний. 6. Типы периферийных интерфейсов, протоколы и форматы данных. В первом приближении МПС является иерархической структурой и состоит из трех функциональных подсистем. Базовая организация МПС фон – Неймановского типа включает подсистему центрального процессора (CPU), подсистему основной памяти (М -memory) и подсистему ввода-вывода (I/O – input/output), объединенных магистралью или системной шиной. Рис.2.1. Основные функции подсистем: подсистема CPU обеспечивает общее управление МПС, выполнение команд и синхронизацию работы модулей; подсистема М обеспечивает хранение исполняемых программ и обрабатываемых данных; подсистема I/O обеспечивает ввод данных, вывод результатов, а также реакцию МПС на запросы от внешних устройств.

Рис. 3.1 Алгоритм командного цикла микропроцессора.

Организация линейной памяти В отличие от регистровой области память программ и данных, а также область ввода/вывода организованы проще. В большинстве случаев память микропроцессорной системы с точки зрения программиста представляет собой линейно упорядоченный набор m -разрядных ячеек с произвольным доступом к каждой из них; это – линейная или “плоская” память. Каждой ячейке из набора соответствует число, называемое адресом ячейки. Все адреса занимают целочисленный диапазон от 0 до 2n-1, который образует адресное пространство памяти. Разрядность адреса п универсальных МП равна 1б или 32 или 64 бита. У микроконтроллеров разрядность адреса может принимать и другие значения, например 12, 14 бит. Разрядность самой ячейки m всегда кратна 8 бит, то есть память имеет байтовую организацию.

Одним из примеров МПС с памятью линейной организации байтового типа является 8-разрядная система на базе микропроцессора 8085. Команды этого микропроцессора могут напрямую обращаться к пространству памяти емкостью 216 = 64К байт. Ячейки памяти имеют шестнадцетиричные адреса в диапазоне 0000 – FFFF. В дальнейшем память МПС будет представляться таким образом, чтобы ячейки со старшими адресами располагались ниже, чем с младшими. Нумерация отдельных разрядов в ячейке производится справа, налево начиная с нуля, при этом разряд с нулевым номером является младшим в байте, а с номером 7 – старшим. Такую же организацию имеет и область ввода - вывода, только порты имеют адреса в диапазоне

Рис. 3.4. Организация линейной памяти.

Команды и их операнды располагаются в соседних ячейках пространства памяти. Адресом объекта (команды) обычно служит наименьший из адресов ячеек, занимаемых им. Операция обращения к памяти предполагает считывание или запись всего объекта как единого целого. Например, слова в памяти МПС на базе МП 8085 хранятся в двух соседних байтах. Старшая часть слова занимает байт со старшим адресом, а младшая – байт с младшим адресом. При этом адресом слова служит адрес младшего байта. Часто организация памяти предусматривает определенные ограничения на возможное расположение много байтовых объектов. Например, слова в памяти могут находиться только по четным адресам. Тогда при доступе к слову значение младшего разряда его адреса, указывающего на байт в слове, во внимание не принимается, т. е. такая память имеет границу слов. Порядок расположения байтов внутри слова стандартный: сначала младший, затем старший байт слова. При необходимости расширить объем памяти за пределы адресного пространства используют дополнительные аппаратные средства. Универсальные 16 – 32 разрядные МП содержат специальные аппаратные средства для организации страничной или сегментной памяти, и эта операция производится штатным способом.

Несмотря на существующую тенденцию по переходу к закрытой архитектуре МК, в некоторых случаях возникает необходимость подключения дополнительной внешней памяти (как памяти программ, так и данных). Для этого можно воспользоваться одним из вариантов диспетчера памяти. В простейшем случае он представляет собой программно-доступный регистр, который должен располагаться в пространстве ввода/вывода. В него заносится номер активного в данный момент банка памяти, причем объем банка может равняться объему адресного пространства МП (2n). Очевидно, в каждый момент времени процессору доступен только один банк. При необходимости перехода в другой банк памяти МП должен предварительно выполнить программную процедуру (часто всего одну команду) переключения номера используемого банка. Рис. 3.5.

Рис. 3.5. Организация расширенной памяти.

Структура микросхем ЗУ.

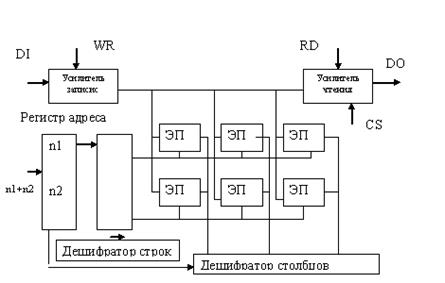

Микросхема запоминающего устройства содержит некоторое число N ячеек, в каждой из которых может храниться слово с определенным числом разрядов n. Ячейки последовательно нумеруются двоичными числами. Номер ячейки называется адресом. Если для представления адресов используются комбинации m-разрядного двоичного кода, то число ячеек в ЗУ может составить N=2m. Количество информации, которое может храниться в ЗУ, определяет его емкость. Емкость можно выражать числом ячеек N с указанием разрядности n хранимых в них слов в форме N * n, либо ее можно определять произведением N и n: M = N . n бит. Часто разрядность ячеек выбирают кратной байту (1 байт равен 8 битам). Тогда и емкость удобно представить в байтах. Большие значения емкости часто выражаются в единицах Кбайт и Мбайт. Например, Кбайт = 210 = 1024; Mбайт = 220байт =210 Кбайт. Емкость 64Кбайт означает емкость, равную 64 . 1024 . 8 бит. Второй важной характеристикой ЗУ является его быстродействие. Быстродействие ЗУ определяется двумя параметрами: временем выборки tb, представляющем собой интервал времени между моментом подачи сигнала выборки и появлением считанных из ЗУ данных на выходе, и временем цикла записи, измеряемом от подачи сигнала выборки при записи до момента, когда допустимо следующее обращение к памяти. Каждая микросхема ЗУ кроме времени обращения и емкости характеризуется потребляемой мощностью, набором питающих напряжений, типом корпуса (числом выводов). Микросхемы ППЗУ дополнительно характеризуются временем хранения записанной в них информации (по истечении которого хранящаяся в ячейках информация может самопроизвольно измениться), допустимым количеством циклов перезаписи (после чего микросхема считается негодной для использования). Основной составной частью микросхем ОЗУ и ПЗУ являются массивы элементов памяти (ЭП), объединенных в прямоугольную матрицу накопителя. Каждый ЭП имеет свой адрес и может хранить или 1 бит информации или целое слово. Для обращения к ЭП необходимо его выбрать с помощью кода адреса, сигналы которого подводят к адресным входам микросхемы памяти.

Доступ к произвольному ЭП(j) производится с помощью прямоугольного дешифратора, состоящего из двух обычных линейных дешифраторов, причем n2 адресных линий заводится на дешифратор столбцов, а другие адресные n1 линии подключены к дешифратору строк. Количество строк и столбцов будет соответственно равно 2(n1) и 2n2, т.е. общее количество, обслуживаемых ЭП, равно 2(n1+n2).

Рис. 3.7. Организация микросхемы статического ОЗУ.

Хотя и ОЗУ и ПЗУ допускают обращение к любому ЭП в произвольном порядке и являются запоминающими устройствами с произвольной выборкой, обозначение RAM по традиции, используется только для ОЗУ. Для ПЗУ применяют обозначение xxRОM, где ROM (Read only memory) – память для чтения. Микросхемы ОЗУ также разделяют по типу ЭП: на статические ОЗУ (SRAM) и динамические ОЗУ (DRAM). В статических ОЗУ в качестве ЭП применяются статические триггеры на биполярных или МОП-транзисторах, способные при наличии напряжения питания неограниченно долго сохранять свое состояние. Например, в микросхеме 537РУ10 в качестве элемента памяти используется простейший D-триггер-защелка и схема управления. В результате каждый ЭП состоит из восьми триггеров. В динамических ОЗУ ЭП выполнены на основе микроконденсаторов в интегральном исполнении, размеры которого значительно меньше D-триггера статической памяти. По этой причине, при одинаковых размерах кристалла, информационная емкость DRAM выше, чем у SRAM. Количество адресных входов и габариты должны увеличиться. Чтобы не допустить этого, адресные линии внутри микросхемы разбиваются на две группы, например старшая и младшая половина. Две одноименные k-линии каждой группы подключаются к двум выходам внутреннего k-го демультиплексора "1 в 2", а его вход соединяется с k-ым адресным входом микросхемы. Количество адресных входов, при этом уменьшается в два раза, но зато передача адреса в микросхему должна производиться, во-первых в два приема, что несколько уменьшает быстродействие, и во-вторых потребуется дополнительный внешний мультиплексор адреса. Такие ЭП не могут долгое время сохранять свое состояние, определяемое наличием или отсутствием электрического заряда, и поэтому нуждаются в периодическом восстановлении (регенерации). В процессе хранения бита конденсатор разряжается. Чтобы этого не допустить заряд необходимо поддерживать. Для этого используют различные схемы регенерации. Микросхемы динамических ОЗУ имеют большую емкость и дешевле, чем статические ОЗУ. Это обусловлено меньшим числом компонентов в ЭП и значительно более плотным их размещением в кристалле. Однако динамические ОЗУ сложнее в применении, поскольку нуждаются в организации принудительной регенерации, в дополнительном оборудовании и в усложнении устройства управления. Динамическое ОЗУ отличается от статического ОЗУ: 1) мультиплексированием адресных входов, 2) необходимостью регенерации хранимой информации, 3) повышенной емкостью (до нескольких Мбит), 4) более сложной схемой управления. На рисунке 3.8 внизу приведена структура БИС динамического ОЗУ. Микросхемы ПЗУ также имеют матричную структуру накопителя. Микросхемы РПЗУ допускают многократное, до сотен тысяч, циклов перепрограммирования на рабочем месте пользователя. Это свойство обеспечивается применением ЭП на МОП транзисторах с "плавающим затвором". В режиме программирования, на выбранный по адресной шине ЭП, куда необходимо записать ноль, подается импульс. Стирание осуществляется УФ-излучением (EPROM), либо электрически (EEPROM). При этом все ячейки переводятся в состояние "1". Записанная информация сохраняется в течение нескольких лет.

Рис. 3.8. Структура БИС динамического ОЗУ

В однократно программируемом ПЗУ (OTP,PROM) функции ЭП выполняют перемычки в виде проводников, диодов или транзисторов между шинами строк и столбцов в накопителе. В такой матрице наличие перемычки соответствует 1, а ее отсутствие – 0. Все типы ПЗУ имеют словарную организацию. Совокупность всех ЭП (j), в которой размещается слово, имеет свой адрес и называется ячейкой памяти ЯП.

Рис. 3.8. Структура БИС однократно программируемого ПЗУ. Для любого значения адресных сигналов А0 – Аn-1 найдется единственный выход дешифратора "i" на котором сигнал Yi = 1, на остальных выходах будут нули. Потенциал базы j-транзистора будет зависеть в этом случае только от наличия или отсутствия перемычки fi. Если перемычка есть (fi=1), то на базе высокий уровень сигнала, транзистор открыт и выходной сигнал DOj = 0. Если перемычки нет (fi=0),то DOj=1.Пережиганием перемычек в соответствующих j-битах всех адресов, в микросхему записывается программа и/или данные. Имеются также запоминающие устройства с последовательным доступом SERIAL EPROM. SERIAL EPROM работают в режиме последовательного битового обмена; оснащаются тактовым входом для синхронизации и одной или двумя линиями данных. Эти микросхемы имеют специальный интерфейс. Их трудно использовать без микропроцессора, снабженного таким же интерфейсом. Однако в комплекте они очень удобны, так как сокращается число линий и упрощается организация обмена. Обычно SERIAL EPROM используют для хранения небольшого количества установочных параметров, даты и т.д.

Регистры и их типы. Основным архитектурным компонентом МПС, определяющим и организацию взаимодействия с CPU модулей системы и организацию вычислительного процесса в целом, является структура регистровой области CPU. Регистры МП можно рассматривать как скоростное ОЗУ малой емкости, предназначенное для хранения адресов и данных и входящее в состав CPU. Регистров относительно немного, поэтому команды работы с регистрами имеют компактный код. Короткая адресация регистровой области и быстрый доступ к ней обеспечивают создание эффективно исполняемых программ. Регистры МП функционально неоднородны: одни регистры служат для хранения данных или адресной информации, другие - для управления работой CPU. В соответствии с этим все регистры можно разделить на регистры данных, указатели и регистры специального назначения. Регистры данных участвуют в арифметических и логических операциях в качестве источников операндов и приемников результата, адресные регистры или указатели используются для вычисления адресов данных (операндов) и команд, расположенных в основной памяти. Специальные регистры служат для индикации текущего состояния CPU и управления режимами работы CPU. Функциональная специализация регистров в свою очередь определяет систему команд CPU. При слабой специализации часть регистров обычно применяется для хранения, как операндов, так и адресов. Если при этом разрядность шин адреса и данных совпадает, например 16/16, то их называют регистрами общего назначения (РОН). Функциональная неоднородность регистров связана с широким использованием неявной (подразумеваемой) адресации регистров. Неявная адресация, в свою очередь, порождает компактный код команд CPU, что, в конечном счете, приводит к созданию коротких программ. Но функциональная специализация регистров затрудняет программирование, так как требует учета особенностей организации регистрового набора, присущих данному CPU. Однако в результате объектный код команд исполняется быстрее и для его хранения требуется меньшая память.

Адресные регистры. А дресные регистры - регистры указатели применяются для реализации различных методов непрямой (вычисляемой) адресации данных. Например у некоторых CPU, регистр косвенного адреса DP (Data Pointer) содержит непосредственно адрес операнда, регистр базы ВР (Base Pointer) используется для хранения начальных адресов массивов и записей, содержимое индексного регистра Х (Index) является относительным адресом (индексом) операнда. Среди адресных регистров следует также отметить регистры автоинкрементной и автодекрементной адресации, которые автоматически увеличивают или уменьшают свое состояние до или после выполнения операции доступа в соответствии с длиной адресуемого ими операнда, и регистры расширения адресного пространства или указатели сегментов и страниц. Очень важной является функция хранения адреса следующего элемента программной последовательности, подлежащего выборке в очередном машинном цикле. Эту функцию выполняет программный счетчик (РС). Большая часть команд CPU выполняется последовательно, в порядке возрастания адресов памяти. Во время выборки очередной команды содержимое РС увеличивается на 1 или 2 для указания адреса следующего байта или слова в последовательных ячейках памяти. При этом процесс адресации следующего элемента командной последовательности, как правило, осуществляется неявно. В типовой команде, какие - либо сведения об адресе следующей команды отсутствуют. Поэтому функция РС возлагается на конкретный регистр, содержимое которого автоматически инкрементируется после очередной выборки элемента командной последовательности. Изменение последовательности процесса выборки команд должно осуществляться специальными командами передачи управления CPU. Эти команды выполняют загрузку в РС адреса, который может отличаться от адреса следующей команды.

Стек. Частным случаем регистра с авто модификацией является указатель стека SP (Stack Pointer). Он необходим для организации системного стека, который предназначен для хранения адресов возвратов и состояний процессора при вызове подпрограмм и обслуживании прерываний. Стек может также использоваться для временного хранения локальных переменных и передачи входных или выходных параметров при вызовах подпрограмм. Стек - это область памяти с доступом типа «последний пришел - первый вышел» или LIFO. Стек обычно заполняется в сторону уменьшения адресов, при этом указатель стека показывает на последнюю заполненную ячейку стека - вершину стека TOS (Top of Stack). Такой стек называется типовым, так как именно он применяется в большинстве МПС. При записи в стек нового элемента данных (операция PUSH) содержимое SP уменьшается на 1 или 2 в зависимости от длины элемента (байт или слово) и затем используется в качестве адреса новой вершины, в которую заносится элемент. При считывании элемента данных из стека (операция РОР) сначала считывается содержимое TOS, а затем содержимое SP увеличивается на 1 или 2 для адресации новой вершины стека. Работа стека показана на рис. 4.1.

Рис. 4.1. Работа стека при вызове подпрограмм.

Исключительные удобства, предоставляемые стеком при вызове подпрограмм, привели к тому, что практически все современные CPU имеют встроенные средства для его построения в виде SP и соответствующих команд CPU. При использовании стека для хранения локальных переменных и обмена параметрами между вызываемой и вызывающей процедурой может оказаться полезным специальный адресный регистр, указывающий на начало области параметров в стеке. Регистр с таким функциональным назначением называется указателем кадра FP. Действительно, значение SP непрерывно меняется, поэтому применять его в качестве точки отсчета при доступе к данным в стеке крайне неудобно. Процедуру доступа можно значительно упростить, если функцию точки отсчета отдать специально зарезервированному для этой цели указателю FP, который принадлежит к классу базовых регистров.

Специальные регистры. При выполнении многих команд АЛУ, кроме результата операции еще генерирует ряд двоичных сигналов - признаков, дополнительно характеризующих результат операции. Функцию хранения этих признаков выполняет специальный регистр признаков (флагов) RF. С каждым признаком результата операции связана одноразрядная переменная - флажок, состояние которой отображает соответствующий бит RF. В состав этого регистра включаются также некоторые другие флажок, характеризующие текущее состояние или режим CPU. Регистр признаков RF вместе со счетчиком команд PC часто объединяют в слово состояния программы PSW (Program Status Word). У первых микропроцессоров был минимальный набор флажков-признаков результата операции: CF - флажок переноса из старшего разряда АЛУ. Флажок CF используется наиболее часто. ZF - флажок признака нуля. SF - флажок знака результата. Применяется при целочисленной арифметике со знаком AC – флажок дополнительного переноса или переноса из младшей тетрады. OF - флажок арифметического переполнения. РЕ - флажок четности результата.

Рис. 4.2. Формат регистра флагов RF.

Бывает очень удобно, если поле условия RF содержит один или несколько флажков пользователя, функциональное назначение которых определяет он сам. Обычно эти флажки служат для связи между отдельными частями программы. В системе команд любого CPU есть команды условного перехода или команды тестирования. Каждая такая команда проверяет состояние определенного флажка RF. В зависимости от этого или происходит изменение последовательности процесса выборки команд или выполняется следующая команда. Таким образом, организуется ветвление программы. В состав PSW может входить также ряд специальных флажков, управляющих работой CPU и устанавливающих, например: маски и приоритеты прерываний, условия реакции на прерывания или флажок пошаговой трассировки. Упаковка всех флажков в одно слово дает возможность организовать их быструю засылку в память (стек) с последующим восстановлением. У более сложных CPU специальных регистров может быть несколько.

Регистры данных. Наиболее типичным представителем регистров данных является аккумулятор А, который используется для временного хранения исходных операндов и промежуточных результатов. С аккумулятором связано большинство команд арифметической и логической обработки. Ссылка на него, как правило, производится неявно с помощью кода операции. Неявная адресация позволяет не указывать в командах местоположения одного из операндов и (или) результата операции, что существенно уменьшает длину их кода. Это очень важно в условиях ограниченной пропускной способности системной магистрали, особенно для 8-разрядных МПС. Поэтому большинство первых CPU, имели аккумулятор и были ориентированы на его интенсивное использование. В составе CPU может находиться один или несколько аккумуляторов. Так, у микропроцессора МС6809 два аккумулятора - А и В. Такие CPU имеют одноадресную систему команд, так как в коде команды явно указывается адрес лишь одного операнда. При этом предполагается, что источником другого операнда служит аккумулятор. Он же, как правило, применяется и для хранения результата операции: Другим вариантом регистров данных являются рабочие регистры. В отличие от аккумулятора они адресуются явно (R0-RN) и могут интерпретироваться как сверхскоростные регистровые ОЗУ данных. Рабочие регистры могут использоваться в операциях как совместно с аккумулятором, гак и без него. Если рабочие регистры совмещают свою функцию хранения данных с функцией их адресации, то в этом случае они приобретают функции РОН. В командах тогда допускается только один операнд, хранящийся в памяти МПС, тогда как другой должен находиться в регистровой области. В архитектуре с рабочими регистрами для реализации быстрого доступа к промежуточным данным часть основной памяти данных обычно размещена на одном кристалле с CPU. В ряде CPU, предназначенных для работы в реальном масштабе времени, могут быть предусмотрены два или даже четыре набора рабочих регистров, один из которых резервируется для системных целей или обработки прерываний, а все остальные - для прикладных задач пользователя. В каждый момент времени доступен только один набор рабочих регистров, выбираемый специальным указателем WP. Выпускаемые промышленностью CPU обычно являются результатом компромиссного выбора между несколькими типами организаций и, следовательно, могут быть отнесены к тому или иному классу лишь условно. Микропроцессоры выпускаются в виде семейств, в которых на одном ядре, содержащем типовой набор регистров выполнены различные по параметрам CPU. В таких семействах, как правило, варьируются параметры размещенной на кристалле памяти и периферии.

Примеры регистровых структур. Классический набор регистров с аккумулятором имеет один из первых 8 – разрядных микропроцессоров фирмы INTEL – i8085. Программная модель микропроцессора i8085, раскрывающая его структуру представлена на рис. 4.3.

Рис. 4.3. Регистровая структура микропроцессора i8085.

Помимо аккумулятора А, в нем имеются шесть 8-битных регистров данных: В, С, D, Е, Н и L. В некоторых командах эти регистры можно объединять в регистровые пары (Rp) ВС, DE и HL для работы с 16-битныии величинами, как данными, так и адресами. Кроме того, регистровая пара HL является типовым индексным регистром и применяется в командах для задания косвенной регистровой адресации. Например, команда МОV А, М передает в аккумулятор А байт данных из ячейки памяти (M - memory), адрес которой находится в регистровой паре HL. Признаки результата операции в АЛУ фиксируются в регистре признаков F, который совместно с аккумулятором А образует 16 - разрядное слово состояния программы PSW. Это слово используется в некоторых командах, работающих со стеком, чтобы быстро сохранить и восстановить контекст CPU. Микропроцессор i8085 также содержит два 16-разрядных адресных регистра: программный счетчик PC и указатель стека SP. Эта регистровый набор был расширен у микропроцессора Z80 фирмы ZILOG. Набор регистров Z80 показан на рис.4.4. Рабочие регистры А, В, С, D, E, H и L аналогичны соответствующим регистрам 8085, но в Z80 существует такой же второй набор регистров (А1-L1) и второй регистр флагов F1. Наличие второго набора (банка) регистров значительно ускоряет работу системы при вызове подпрограммы или обработке прерывания, потому что программист может использовать для них альтернативный набор, избегая сохранения содержимого регистра основной программы, например командами включения в стек. Для программной поддержки этого процесса в системе команд Z80 есть две команды, которые осуществляют обмен содержимого всех регистров:

EXX; Обменять BC, DE, H. EX AF, AF; Обменять AF и AF (F обозначает флажки).

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 739; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.119.253.93 (0.085 с.) |