Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Методические указания по выполнению задачи 5.2

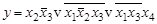

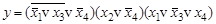

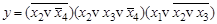

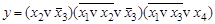

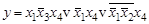

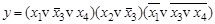

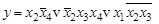

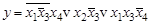

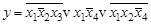

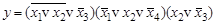

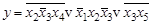

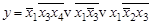

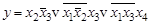

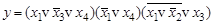

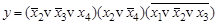

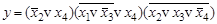

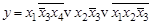

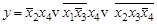

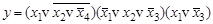

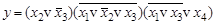

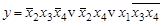

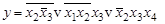

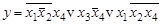

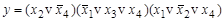

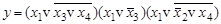

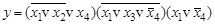

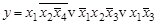

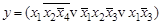

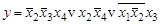

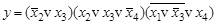

1. Исходную логическую функцию не минимизировать. 2. Для построения схемы устройства можно использовать любые логические элементы, входящие в состав заданной серии ИМС [15, 16, 19]. 3. Вне зависимости от количества используемых логических элементов в ИМС, берется ток, потребляемый всей микросхемой. 4. На принципиальной схеме обозначить входные и выходные сигналы каждого логического элемента, соответствующие заданному набору входных. Задача 5.3 Разработать цифровое устройство, реализующее заданную логическую функцию, на логических элементах заданной серии интегральных микросхем (ИМС). В таблице 6.2 в соответствии с номером варианта заданы: логическая функция; тип логических элементов и серия ИМС. Изобразить принципиальную схему устройства и найти ток I п, потребляемый схемой. Определить состояние выхода устройства (логические “0” или “1”) при наборе входных сигналов: x 1= 1, x 2 = 0, x 3 = 1, x 4 = 0. Таблица 5.3

Продолжение табл. 5.3

Продолжение табл. 5.3

Методические указания по выполнению задачи 5.3 1. Исходную логическую функцию не минимизировать. 2. Заданную логическую функцию предварительно преобра-зовать к требуемому виду с помощью законов алгебры логики [3, 5]: – отрицания-отрицания – де Моргана 3. Для построения схемы устройства использовать только заданные логические элементы, входящие в состав заданной серии ИМС [15, 16, 19]. 4. Вне зависимости от количества используемых логических элементов в ИМС, берется ток, потребляемый всей микросхемой.

5. На принципиальной схеме обозначить входные и выходные сигналы каждого логического элемента, соответствующие заданному набору входных сигналов. Задача 5.4 На входы JK -триггера, изображенного на рис. 5.3, подаются логические сигналы, временные диаграммы которых приведены на рис. 5.4. Заданные характеристики входов и временные диаграммы входных сигналов для каждого варианта приведены в таблице 5.4.

Примечание. В таблице 5.4 использованы следующие обозначения входов JK -триггера: “прям.”, “инв.” – соответственно прямой и инверсный асинхронные входы; “фронт”, ”срез” – синхронизирующий вход С с динамическим управлением соответственно по фронту и по срезу синхронизирующего импульса.

|

|||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 273; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.14.133.148 (0.006 с.) |

.

. Изобразить условное графическое обозначение и временные диаграммы входных и выходных сигналов заданного JK -триггера. Исходное состояние выходов триггера принять: Q = 0;

Изобразить условное графическое обозначение и временные диаграммы входных и выходных сигналов заданного JK -триггера. Исходное состояние выходов триггера принять: Q = 0;  = 1.

= 1.